基于Virtex-6 FPGA的三种串行通信协议测试及对比 (二)

载荷来达到更低的数据包开销。(4KB包载荷下,PCIe 2.0的数据包开销为0.5%)

协议的理论传输速率由通道带宽和协议开销决定,而协议的实际传输速率还受设备本身性能的影响。本测试中,PCIe 2.0 DMA读操作数据传输速率速率高于SRIO 2.0 NREAD的主要原因是服务器对FPGA的PCIe读请求的响应要快于DSP对FPGA的SRIO读请求响应。

(5)设备寻址

PCIe协议中,各设备共享一个PCIe地址空间。整个PCIe地址空间先被分成块,根据后来的下级总线这些块再进一步划分。树形结构中的每个设备在整个地址空间映射中被指定一个地址空间,通过执行全部地址译码来查找设备。在支持带有大容量存储器的设备系统中,这种设备寻址机制不适合灵活拓展。

SRIO采用基于设备ID寻址的方案。采用该方案,使得拓扑结构的变化仅需要更新事务路径中的设备,从而使系统的拓展与拓扑结构的更改比PCIe协议更为灵活。

Aurora 8B/10B协议未定义设备寻址机制。

(6)网络拓扑

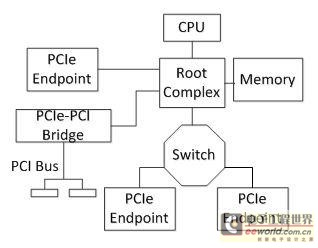

PCIe规定了生成树拓扑结构,这种结构适合于单个主机,多个外围设备通信模式,但限制了端点数量,且不支持任意节点与节点间直接通信。PCIe的典型网络拓扑结构如图15所示。

图15 PCIe网络拓扑结构

SRIO的拓扑结构比PCIe更为灵活,可设计成网型,星型,雏菊链或树形拓扑结构,支持节点对节点通信,各节点间可对等的发起数据传输。

Aurora 8B/10B协议不支持网络拓扑结构。

(7)应用领域

Aurora 8B/10B协议作为Xilinx公司开发的轻量级链路层协议,协议开销小,链路数目和链路线速率选择灵活,适用于两片Xilinx FPGA之间的数据流传输。用户也可在其基础上开发高层协议。但其应用范围较为有限,尚未见在其他芯片中使用。

PCIe 2.0作为PCI总线的继承,带宽,拓展灵活性大大提高,适合于主机与外部设备的互联,在PC/Server平台、VPX平台有广泛应用,如声卡、显示卡、网络设备(包括以太网、Modem)、光纤接口卡、磁盘阵列卡等。

SRIO 2.0作为一种高性能包交换的互连技术,数据传输方式和拓扑结构灵活,为多处理器系统的实现提供便利,广泛用于嵌入式系统内的微处理器、DSP、通信和网络处理器、系统存储器之间的高速数据传输。

7结束语

本文基于Virtex-6 FPGA芯片,对Aurora 8B/10B,PCIe2.0,SRIO 2.0三种串行通信协议进行了速率测试,并通过分析协议开销和协议的流控制机制,计算了三种协议的理论传输速率和协议实际通信效率。结合测试结果和三种协议的具体内容,对三种协议的相关参数和应用领域进行了对比分析。本文测试模块结构的设计可为三种协议的工程实现提供借鉴,协议实际传输速率的测算和协议理论传输速率的分析计算可为三种协议在不同平台和工作模式下的测试提供参考。在进行雷达信号处理机数据传输方案的设计时,可参照本文对三种协议的性能分析,根据系统自身的特点及对数据传输速率的要求,合理选择协议类型和协议的工作模式。

Virtex-6FPGA串行通信协 相关文章:

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)