巧用DC/DC转换器以满足FPGA电源设计需求

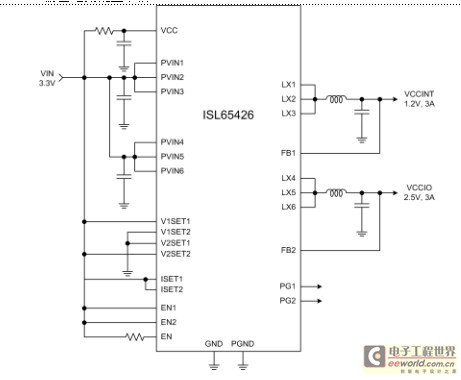

着给定电源设计对负载电流的要求发生变化,可以以最小的努力来重新调整设计。因为ISL65426包含内部电源开关,而且是内部补偿,因此通道之间的负载电流分配的变化通过改变ISET1和ISET2的逻辑电平,以及到芯片的PVIN和LX连接就能实现。图3和图4所示为一些典型的配置。

图3:单电源3A/3A输出电流配置中的ISL65426

图4:单电源4A/2A输出电流配置中的ISL65426

灵活的输出电压选择

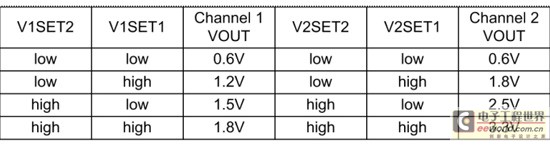

ISL65426能够在不使用外部反馈电阻的情况下规划每个通道的输出电压。V1SET1、V1SET2、V2SET1和V2SET2等四个逻辑引脚从一个通用值清单中为每个通道选择输出电压。实质上是一个2位VID输入,为重新设计和重定目标提供了进一步的便利,因为它允许通过逻辑,而不是通过对电源板及其元件进行物理改变来调整输出电压,从而可以迅速和可靠地实现改变。另外,这个2位VID输入允许对这些系统中的ISL65426转换器通道的输出电压进行数字化控制,而且在这些系统中需要这样的控制。表1列出了输出电压选择。

表1:输出电流配置

表2:输出电压配置

不必使用反馈电阻,简化了设计,减少了元件数量并提高了系统的总体精度。但这种输出电压选择的方便性并未牺牲设计灵活性,因为ISL65426保留了设置输出电压的传统电阻分压器方法。芯片的内部基准电压是0.6V,在使用5V的输出电源时,通过电阻反馈可以把每个通道的输出电压设定在0.6?V之间的任意值。

集成故障保护

ISL65426具备过压、欠压、过流和过温保护机制,以便把全部故障监控和保护功能都完全集成到一个芯片之中,而且不需要使用外部元件。在过压情况下(输出电压高于过压水平――基准电压的115%),ISL65426将主动地努力调节输出电压,使之下降到规定值。在欠压保护情况下,对反馈电压进行监控,并与欠压水平(基准电压的85%)进行比较。如果在一个转换器通道上检测到欠压情形,则一个4位计数器就累加一次。如果在同一个开关周期中探测到两个转换器通道都出现了欠压情形,则该4位计数器就累加两次。每当转换器通道上探测到欠压情形,这个计数器就继续累加。一旦计数器溢出,欠压保护逻辑就把两个转换器都切断。

过流保护电路也采用了一个4位计数器记录过流事件。对每个电源模块中的电流进行测量并与和所用的具体电源模块配置相适应的过流水平加以比较。如果测得的电流超过了过流阈值,一个4位加/减计数器就加1。如果测得的电流在计数器溢出之前降至过流阈值下方,则计数器重置。如果两个转换器通道都在同一开关周期内出现过流现象,则计数器就加2。一旦计数器溢出,两个转换器通道就被切断。如果在同一个周期中测得的两个转换器通道的电流都降至了过流水平的下方,则计数器重置。

最后,在过温保护方面,一个内部温度传感器连续监控ISL65426的节温,如果温度超过150°C,传感器就命令ISL65426关闭两个传感器通道和栓锁(latch off)。

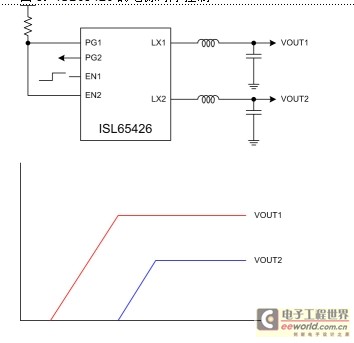

电压监控与电源时序控制

ISL65426的每个转换器通道都具有自己的使能信号和电源良好信号(power-good signal)。这样就可以实现对每个输出电压的单独控制和监控,使电压追踪和电源时序监控成为可能。有两个使能信号――EN1和EN2,用于启用或禁用每个通道。还有一个系统使能信号EN,可以用于同时启动或关闭两个通道。当接收到使能信号而且通道被启用时,一个数字软启动功能通过以20ms的固定间隔来逐渐提高基准电压来提升输出电压。对于电压监控,每个转换器通道都有自己的电源良好信号,当某个通道的输出电压超出调节限度时可以被确定。对于ISL65426的两个输出电压的时序测定是通过把一个通道的电源良好信号连接到另一个通道的使能输入来实现的。在这个配置中,第二个输出当第一个输出处于调节过程中时不会开始软启动周期,如图5所示。

图5:ISL65426的电源时序控制

完整的FPGA电源解决方案

由于配置方便、具有集成的电源器件、效率高、具有集成的故障监控和保护、支持使用陶瓷电容器和RoHS兼容,ISL65426代表一种完整的和环境友好的电源解决方案。在总体FPGA或CPLD系统实施过程中,可以快速、方便及可靠地实施设计变化,从而可以缩短设计周期和减少设计反复。

DC转换 相关文章:

- 技术浅谈:DC/DC转换器中电感器对待机时间的影响(12-12)

- 电源系统管理中数字可编程 DC/DC 转换器的精确度探讨(12-12)

- 详解设计高效的DC/DC转换器(12-12)

- 用于便携式产品的双通道DC/DC转换器(12-09)

- 1A/76V高效MAXPower降压型DC-DC转换器(12-09)

- 超低静态电流升压DC-DC转换器(12-08)