提高FPGA复位的可靠性 你知道多少

电源电路设计中,对FPGA设计中常用的复位设计方法进行了分类、分析和比较。针对FPGA在复位过程中存在不 可靠复位的现象,本文例举了提高复位设计可靠性的几种方法,也就是采用清除复位信号上的毛刺、异步复位同步释放、专用全局异步复位/置位资源和采用内部复 位等方法来提高FPGA复位的可靠性。

对FPGA芯片而言,在给芯片加电工作前,芯片内部各个节点电位的变化情况均不确定、不可控,而这种 不确定且不可控的情况会使芯片在上电后的工作状态出现错误。因此,在FPGA的设计中,为保证系统能可靠进进入工作状态,以及避免对FPGA输出关联的系 统产生不良影响,FPGA上电后要进行复位,且为了消除电源开关过程中引起的抖动影响,复位信号需在电源稳定后经过一定的延时才能撤销,FPGA的复位信 号需保证正确、稳定、可靠。

复位设计方法分类

复位的目的是在仿真时将设计强制定位在一 个可知状态,合理选择复位方式是电路设计的关键。根据与系统时钟域的关系,复位电路可分为同步复位和异步复位。同步复位是指复位信号只在时钟沿到来时,才 有效。否则,无法完成对系统的复位工作。异步复位是指无论时钟沿是否到来,只要复位信号有效,使对系统进行复位。

根据是否存在外部复位端口,复位电路又可分为外部复位和内部复位。外部复位是指复位信号主要来自外部引脚的输入,如复位按钮、电源模块输出等。内部复位信号则是主要由FPGA内部电路产生。

复位设计方法的比较

(1)同步复位

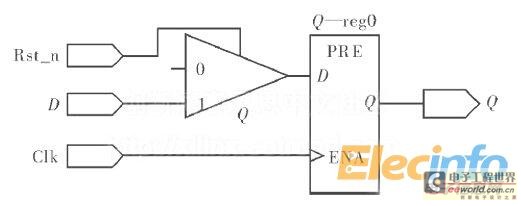

指 定同步复位时,always的敏感表中仅有一个时钟沿信号,只有当时钟沿采集到同步复位的有效电平时,才会在时钟沿到达时刻进行复位操作。若目标器件或可 用库中的触发器本身包含同步复位端口,则在实现同步复位电路时可直接调用同步复位端。然而多数目标器件的触发器本身并不包含同步复位端口,需使复位信号与 输入信号组成某种组合逻辑,然后将其输入到寄存器的输入端。为了提高复位电路的优先级,通常在电路描述时使用带有优先级的if…else结构,复位电路在 第一个if下描述,其他电路在else或else…if分支中描述。复位电路综合后的RTL图如图1所示。

图1 同步复位电路图

根 据同步电路的特点,其电路优点有:同步复位有利于基于周期机制的仿真器进行仿真;使用同步复位可设计100%的同步时序电路,有利于时序分析,其综合结果 的频率较高;(3)同步复位仅在时钟的有效沿生效,可有效避免因毛刺造成的亚稳态和错误。毛刺信号是由FPGA内部结构特征决定的,同步复位在进行复位和 释放复位信号时,仅当时钟沿采到复位信号电平变化时进行相关操作,若复位信号树的组合逻辑出现了某种毛刺,此时时钟沿采到毛刺的概率较低,由此通过时钟沿 采样,可有效过波复位电路组合逻辑产生的毛刺,增强了电路稳定性。

同步复位的缺点有:多数目标器件库的触发器本身并不包含同步复位端口,使 用同步复位会增加更多逻辑资源;同步复位的最大问题在于必须保证复位信号的有效时间,需要一个脉宽延展器以确保复位信号有一定脉冲宽度,由此才能保证所有 触发器均能有效复位。由于同步复位仅当时钟沿采到复位信号时才会进行复位操作,所以其信号的持续时间要大于设计的最长时钟周期,以保证所有时钟的有效沿都 能采样到同步复位信号。事实上,仅保证同步复位信号的持续时间大于最慢的时钟周期是不够的,设计中还需考虑到同步复位信号树通过所有相关组合逻辑路径时的 延时,以及由于时钟布线产生的偏斜。只有同步复位大于时钟最大周期,加上同步信号穿过的组合逻辑路径延时和时钟偏斜延时,才能确保同步复位的可靠。

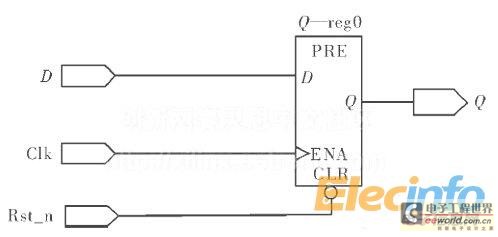

(2)异步复位

指 定异步复位时,只需在always的敏感表中加人复位信号的有效沿即可,当复位信号有效沿到达时,无论时钟沿是否有效,复位均会立即发挥其功能。大多数目 标器件和ASIC库的触发器均包含异步复位端口,异步复位会直接接人触发器的异步复位端口,综合后的RTL图如图2所示。

图2 异步复位电路图

根据异步电路的特点,异步复位的优点有:由于多数目标器件库的触发器都包含异步复位端口,异步复位会节约逻辑资源;异步复位设计简单;对于多数FPGA,均有专用的全局异步复位/置位资源(GSR,GlobalSetReset),还可使用GSR资源,异步复位到达所有寄存器的偏斜最小。

异 步复位的缺点如下:异步复位的作用和释放与时钟沿并无直接关系,异步复位生效时问题并不明显;但当释放异步复位时,若异步复位信号释放时间和时钟的有效沿 到达时间几乎一致,则容易造成触发器输出为亚稳态,形成逻辑错误;若异步复位逻辑树的组合逻

FPGA复位可靠 相关文章:

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)