EMCCD相机数字控制系统的VHDL设计

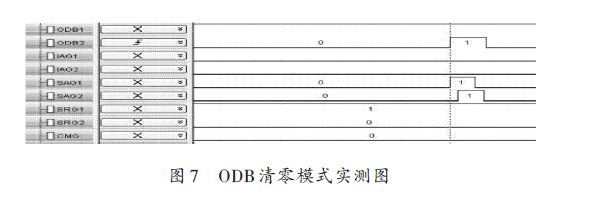

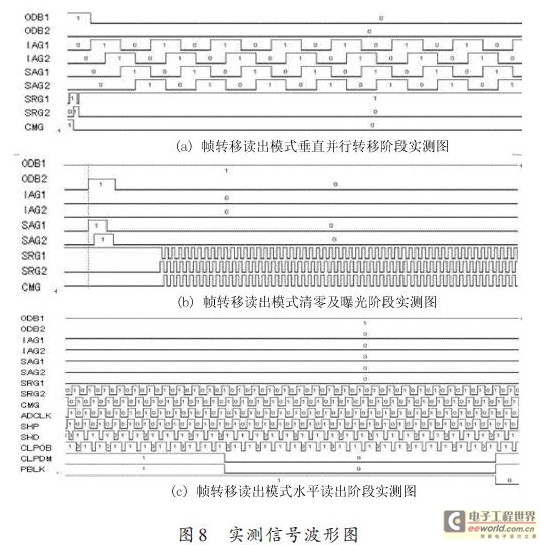

.0环境下设计了相应的C 程序,以便对前面设计生成的EMCCD数字控制器进行测试。实际电路板上进行测试与仿真还是有所不同的。发现有些仿真能顺利得到波形但是在将程序下载到实际电路板上之后,程序却并不运行。需要经过一系列的调整与修改,程序在电路板上才能正常运行,并得到具有正确时序的信号波形。对标准电平的数字信号,测试时使用的是安捷伦公司生产的1693A 逻辑分析仪,对于驱动电路输出的时钟信号,则使用安捷伦公司生产的MSO6012A 示波器。由于篇幅有限,这里仅给出部分测试波形,如图7~图9所示。

图7为ODB清零模式实测信号波形图,图8为帧转移读出模式垂直转移阶段、清零及曝光阶段、水平读出阶段的信号波形图,其中AFE 的驱动信号波形在图8(c)中。由于波形的名字显示太小,看不清楚,故只截取了波形图,信号名是单独编辑上去的。通过观察实测波形,其中垂直转移信号IAG1,IAG2,SAG1,SAG2频率为1.046 MHz,水平读出信号SRG1,SRG2及电子倍增信号CMG 频率为3.125 MHz.这些都符合数据手册上的要求。将实测波形、仿真波形与数据手册上的要求进行对比,说明实测波形时序是正确的。逻辑控制信号经FP-GA产生,输入相应驱动电路,产生控制信号。其中电荷倍增驱动电路是实现EMCCD器件片上增益功能的关键。

这里采用的是TI公司生产的TC253芯片及该公司推荐的电荷倍增高压驱动电路,并进行了一定修改。

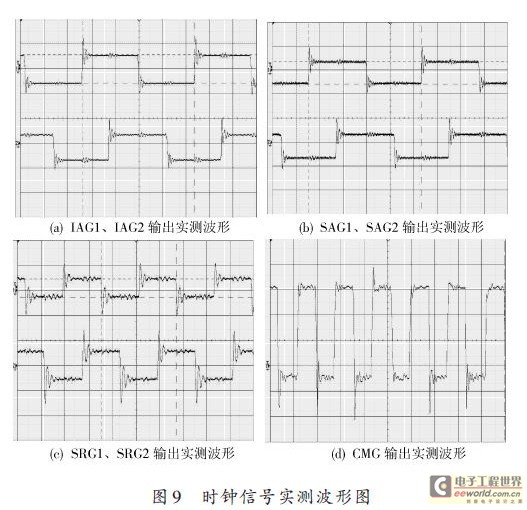

由于IAG1,IAG2信号的频率较高而驱动电路中三极管的开关特性非理想,造成了输出信号的占空比出现一个小的固定偏差。以这个实测的偏差作为时序修正量,在VHDL程序的时钟生成部分进行少量修改,即可改变FPGA的输出(亦即驱动电路输入)信号的占空比,或者说,预先对其进行修正;然后利用三极管开启和关断时间的不同,使最后从驱动电路输出的时钟的占空比基本达到50%.这种方法与段帷用硬件电路进行调整的,电路结构简单,且易于实现,但调节的精度稍差。经过时钟驱动电路后的部分垂直、水平时钟信号实测波形如图9所示,其中,图9(a)~(c)中波形的纵坐标10 V/div,图9(d)中则为5 V/div.

图9(a)中IAG1(上)、IAG2(下),频率均为1.046 MHz,IAG1 高电压为5.3 V,IAG2 高电平为3.1 V,IAG1 低电压为-6.2 V,IAG2低电压为-7 V;图9(b)中SAG1(上)、SAG2(下),频率均为1.046 MHz,高电压均为3.3 V,SAG1 低电压为-7 V,SAG2 低电压为-6.9 V;图9(c)中SRG1(上)、SRG2(下),频率均为3.125 MHz,高电压均为5.0 V,SRG1低电压为-4.3 V,SRG2低电压为-5.6 V;图9(d)中为CMG 的输出实测波形,频率为3.125 MHz,高电压为15 V,低电压为-3.0 V.这些说明实测信号基本满足数据手册的要求。波形中的欠阻尼振荡是因为测试时只接了电容负载而没有接阻尼电阻。当插入EMCCD后,硬件上将接入一个小的阻尼电阻,将可有效减小这种阻尼振荡的幅值。

5 结语

通过对所用EMCCD器件TC253和模拟信号处理器AD9845B的分析,结合成像系统硬件的具体情况,采用顶层控制底层的VHDL模块设计方法,完成了基于FPGA的EMCCD数字控制系统的设计与实现工作。仿真和实测的信号波形在逻辑与时序两方面都完全达到了成像控制与图像采集系统的控制要求。这说明对基于TC253和AD9845B的EMCCD成像系统的分析及其时钟信号的VHDL 设计方法是正确的。另外,在较高频率下,信号经过多级输出或驱动电路后,可能会出现时序偏差。采用实测的方法获得这个偏差,以此作为VHDL信号时序的修正量,实现了时钟驱动波形的正确输出。

这也突显以VHDL进行FPGA逻辑与时序控制电路设计的优点。

EMCCD相机数字控 相关文章:

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)