差分运算放大器驱动器实现高分辨率ADC输入过压保护

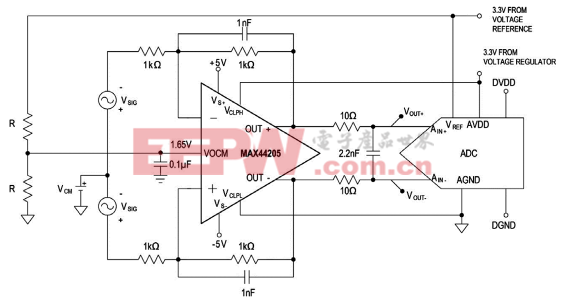

图5 本电路中,不使用外部肖特基二极管或分立式元件对驱动器输出进行箝位

在我们的实验中,进行了两项测试:

1.每路输出上的电压摆幅设置为3.3VP-P,使用1.65VDC

偏置电压每路输入为3.3VP-P,相差180°,两路输入上的实际 差分输入电压(VINDIFF)为6.6VP-P。由于增益为1V/V,所 以每路输出也为3.3VP-P,相差180°,输出上的差分电压为6.6VP-P (图3)。

从图3的示波器曲线中可以看出,由于每路输出的最大 和最小电压分别为3.3V和0V,尚未启动箝位,如VOUT曲线 所示。这是可以理解的,二极管尚未导通来保护ADC。

2. 每路输出上的电压摆幅设置为5VP-P,使用1.65VDC

偏置电压每路输入为5VP-P ,相差180°(图4)。两个输入上的实 际差分输入电压(VINDIFF)为10VP-P。由于增益为1V/V,每 路输出则应为5VP-P,相差180°;输出上的差分电压应为10VP-P。每路输出在1.65VDC偏压下的5VP-P意味着输出摆 幅为4.15V至-0.85V。实际上,只要每路输出超过3.3V加二极管正向压降,二极管即打开,开始导通,将驱动器输出电压箝位到3.92V。类似地,二极管也将驱动器输出箝

位到-0.8V。

在图2的配置中,肖特基二极管导通的硬箝位 状态期间,消耗的电源电流大约为15mA。大多数 ADC的输入电压绝对最大额定值高于上轨0.3V以 及低于下轨- 0.3V。

无外部分立式二极管硬箝位

现在,我们介绍不使用外部二极管的驱动器 输出过压保护电路(图5)。该方案不仅节省PCB空 间,也节省肖特基二极管的成本。图5所示的电路 与图2相同,但缺少了四个二极管。

图5中的MAX44205运算放大器有两个输出箝位引脚, VCLPH和VCLPL,可用于将输出电压限制到预设电压。将 ADC电源轨连接到这些箝位引脚时,驱动器输出被箝位到 ADC电源轨范围之内,与驱动器的输入电压摆幅无关。

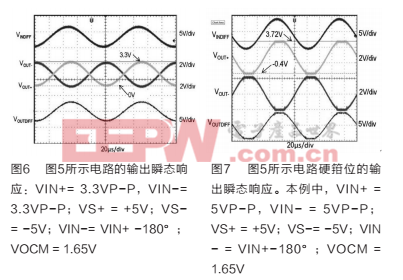

同样,我们进行了两项测试:

1. 每路输出上的电压摆幅设置为3.3VP-P,使用1.65VDC

偏置电压

同样,每路输入为3.3VP-P ,相差180°(图6)。由于增 益为1V/V,每路输出也为3.3VP-P,相差180°。在示波器曲 线中(图6),驱动器每路输出的摆幅为3.3V至0V,与ADC电压轨严格相同,所以至此尚未进行箝位。

2.每路输出上的电压摆幅设置为5VP-P,使用1.65VDC

偏置电压

每路输入为5VP-P,相差180°;两路输入上的实际差 分输入电压(VINDIFF)为10VP-P,如图7所示。由于增益为

1V/V,每路输出也应为5VP-P,相差180°。同样,每路输 出在1.65VD C偏压下的5VP-P意味着输出摆幅理论上应为

4.15V至-0.85V。MAX44205运算放大器对输出进行箝位,将 其正向摆动限制到3.72V,负向摆动限制到-0.4V,如VOUT+ 踪迹所示(图7)。

MAX44205运算放大器拥有专利箝位方法,硬箝位状态 下通过VCLPL的耗流只有92μA。与图4所示分立式设计的毫 安级电流持续10s相比,这毫不逊色。MAX44205在箝位期间 的输出电压限值为VCLPH + 0.34和VCLPL - 0.42。不建议严 格箝位到ADC的电源轨,因为驱动器输出需要无失真摆动 到ADC的电源轨。如果将驱动器输出严格箝位到VCLPH和 VCLPL,箝位电路需要在输出等于ADC电源时打开,这将造 成失真。

- 用集成式8开关无闪烁驱动器控制矩阵式LED前灯中的单个LED(下)(03-24)

- 基于1602液晶电压驱动器应用于proteus仿真(12-12)

- 用集成式8开关无闪烁驱动器控制矩阵式LED前灯中的单个LED(上)(03-23)

- 三相PWM电机驱动器A3936及其应用[图](12-09)

- 电源IGBT驱动器短路保护测试方法(12-08)

- 如何确定步进电机驱动器电压、电流及配用(12-07)