时钟技术的未来发展:向分组网络转型

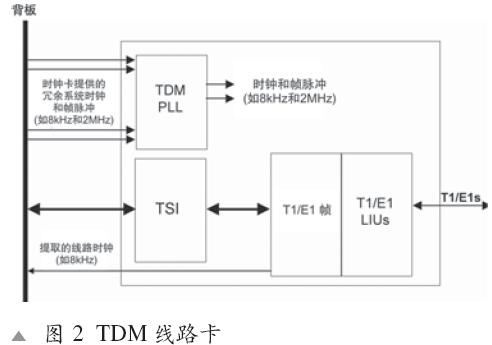

用的简化型线路卡,可支持电路交换网络。出于简化目的,我们不妨假定该线路卡是通过 T1/E1 线路提供 NxDS0 语音服务。线路卡上的 PLL 可以是数字 PLL、模拟 PLL 或者数字与模拟 PLL。

线路卡上 PLL(DPLL、APLL 或数字与模拟 PLL)的主要要求是监控来自时钟卡的系统时钟并在发生故障时执行无中断参考转换。线路卡上的 PLL 还必须执行抖动衰减,从而为线路卡器件提供低抖动时钟,以确保操作无故障并符合相关标准。

如前所述,线路卡上的 PLL 锁定于来自时钟卡之一的背板参考时钟,随后其还将为 TSI、成帧器和 LIU 生成线路卡上所有必需的频率。上述频率通常分别为 8 kHz、1.544 MHz 和 2.048 MHz。我们假定背板参考时钟频率为 8 kHz 和 2 MHz。

线路卡还能从T1/E1线路提取时钟参考,并将其提供给时钟卡。通常它会是8 kHz的频率参考。

分组线路卡(改进版)

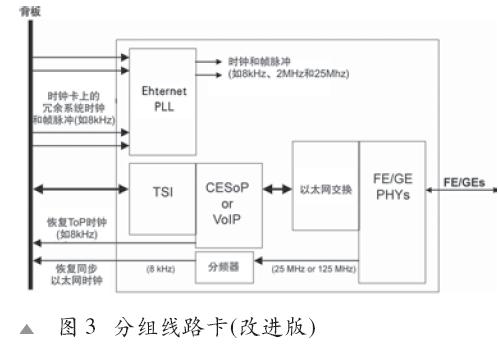

图3 给出了一款简化线路卡,该线路卡不仅具有以太网接口,而且还能满足传统 TDM 线路卡现有系统背板设置的要求。背板的时钟和数据接口保持不变。NxDS0数据仍通过 TSI 传输,提取的线路卡时钟以及背板时钟卡时钟仍为 8 kHz 和 2 MHz。

不过,就线路卡本身而言,VoIP 或 CESoP (电路仿真分组业务)处理器协同以太网交换机与 FE/GE PHY 在以太网/IP网络上传递 NxDS0 语音服务。

就时钟技术而言,改进的 PLL 必须锁定于来自时钟卡的传统 TDM 频率,并同时生成 TDM 时钟频率和分组时钟频率(如25 MHz)。就性能而言,用于物理层同步的分组时钟频率比单纯的 TDM 频率对抖动性能的要求更高。抖动生成与衰减会对改造的PLL提出更高要求。

从背板到网络接口存在许多可能的时钟路径。首先,改进的 PLL 可为 FE/GE PHY生成 25 MHz 频率,以实现物理层同步。其次,改进的 PLL 还能为 CESoP 或 VoIP处理器生成 8 kHz 或 1.544 MHz/2.048 MHz 频率,进而为分组网络生成带嵌入时钟信息的分组。

从网络到背板也存在多种可能的时钟路径。首先,FE/GE PHY 可从物理线路提取频率为 25 MHz 或 125 MHz的时钟,进而分解为 8 kHz 频率并提供给背板上的时钟卡。其次,CESoP 或 VoIP 处理器能根据带嵌入时间戳的传送进来的分组进行自适应时钟恢复,从而为背板提供参考时钟。

分组线路卡(新型)

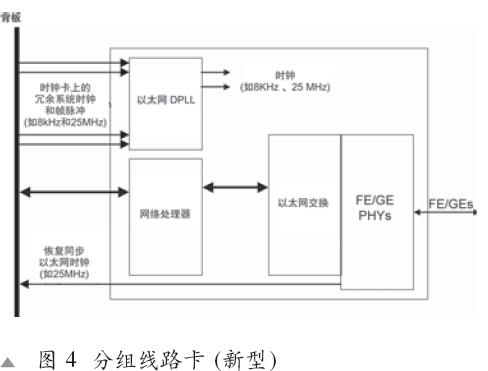

图4 给出了不带传统 TDM 背板且完全采用分组技术的设备。在此情况下,时钟很可能完全采用 25 MHz (或其倍数)的频率。这里给出的结构图显示了带 GE/FE接口的分组线路卡。

FE/GE PHY 从物理层提取 25 MHz 或 125 MHz 频率,以此作为网络参考提供给时钟卡。时钟卡依次选择一个线路卡参考,清空时钟,然后为所有线路卡提供统一的25 MHz (也可能为 8 kHz)时钟频率。

以太网 PLL 会锁定于 25 MHz 的时钟频率,并为线路卡提供所有必需的时钟。此外,以太网还可提供 PHY 使用的 25 MHz 时钟,以便对以太网物理层进行时钟,进而确保网络下一节点的时钟同步。

结语

同步技术以前是在不断提高的带宽与时钟频率的推动下慢慢发展的。而现在,网络从电路交换技术发展到了分组交换基础设施,这时,电信网络的时钟和同步技术都将发生巨变。

对基于分组交换技术的设备而言,将需要时钟引擎和时钟接口来支持各种新的时钟技术。一层物理层同步技术与二层交换技术、三层路由技术将相互结合。随着 IEEE 1588 和 NTP 规范的发展,新的同步技术已开始出现,以满足电信网络的各种需求。

- WLAN与VoIP技术结合促进企业通信发展(02-11)

- IP微波:现代应急通信的新利器(12-15)

- IP微波助力光网成环(05-18)

- iPhone代替信用卡Visa推出配件In2Pay(05-19)

- 狂人设计之iPhone 4(07-05)

- 未来iPhone:手上投影 (10-25)