FPGA基软件无线电

来调谐所关心的信道。集成IP核以保证这样复杂的系统可用于行业标准单PMC卡。

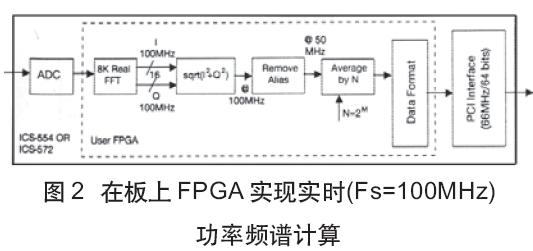

ICS已把8K实时FET引擎和功率检测及频谱平均集成在一起(图2)。

3m门Virtex II FPGA很容易支持具有功率检测和可编程平均的8K FET引擎。

改进C/I 的智能天线和相控阵雷达射束形成器

具具有大量元件和C/I改进的智能天线的相控真雷达正在成为下一代商用无线系统的共同关心的问题。这些系统可以处理大量带宽并能来回传送数据。建造一个能在多DDC间同步和多模块间高速数据传输同步系统。

一个在40和20MHz带宽实现的2×2射束形成器示于图3。用两个ICS-554采集4路模拟信道。对于20MHz带宽,每个ICS-554产生4个单独的射束,其中两个射束送到其他数据采集板卡。每个板卡把内部产生的2个单独射束与以其他ICS-554接收的2个单独射束组合产生2个完整射束。对于低电压晶体管—晶体管逻辑(LVTTL)400MBps,每个方向板之间的数据传输是200MBps。希望用低电压差分传输(LVDS)接口能显著地增加数据传输,增加带宽。

在Pn4PMC用户I/O上高速数据传输

在某些应用中,对于系统集成人员从商用现成PMC模块用用户定义的协议传输高速数据是更方便的,这使系统总线对于其他功能是空闲的。这样一种协议通常用在前面板数据口(FPDF)协议,这是一种ANSI/VITA(美国国家标准委员会/VME bus行业贸易协会)标准。为了确保高速数据传输,ICS在用户FPGA中已实现发送和接收核来支持PMC模块的Pn4用户I/0连接器的FPDA前面板数据口。因此,系统集成人员经FPDA在ICS PMC模块上有无缝传输数据的方法。其他标准和专利数据传输协议也能在用户FPGA中实现。

在Pn4用户 I/O连接器上用LVDS信号传输可在PMC模块间或从PMC模块到母板实现高速数据传输。

结语

FPGA 正在成为无线电设计的主要部分。正在增加更多功能到FPGA。然而,FPGA和传统DSP及GPP正在共存,而灵活的平台将包括二者的混合。

对待FPGA,设计像执行硬件设计,而不仅是一个软件问题。在任务计划阶段是需要考虑的因素。■(益林)

- 基于FPGA的短波通信接收机(11-19)

- FPGA的低功耗设计(07-06)

- EDA环境衔接测量软件(06-25)

- Altera 28nm FPGA助力NEC提升LTE基站性能(11-19)

- 基于FPGA的BPSK信号载频估计单元设计(09-02)

- FPGA推动5G异构无线网络(09-28)