一种宽带复接器的设计与实现

信息时代的到来使人们需要共享越来越多的信息。随着信息及其需求的爆炸性增长,信息的选择及传输速率成为一个重要问题。有线电视网络有其固有的高带宽特性,适合大容量的数据传输和实时性要求,使宽带数字接入成为可能。在我国由于有线电视网是一个已经存在的接入网络,成本低、可维护性强、频率资源丰富、覆盖面广、用户量大,因而通过有线电视网进行数据广播是目前国内应用领域的一大热点。DVB-C是ETSI(European Telecommunications Standards Institute)提供的基于Cable上数据广播的一整套标准[1,2,3],本文首先介绍DVB-C数据广播系统的基本结构,接着详细分析TS复接器在整个系统中的重要性与功能,然后详细说明利用DSP(数字信号处理器)与FPGA(现场可编程门阵列)相结合的一个实现方案,阐明了其中的设计方法和系统结构。

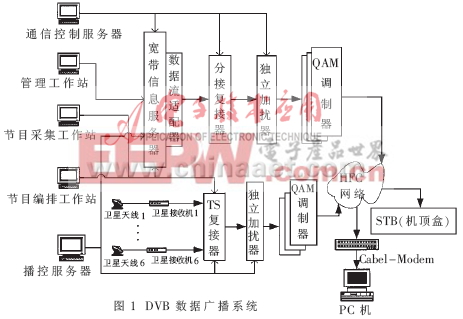

1 DVB-C数字广播系统简介

一个实用的DVB-C广播系统的结构如图1所示[3~6],整个系统可以大致分为三个部分:(1) 信息前端,包括视频服务器、播控服务器、通信控制服务器、用户管理工作站、节目采集工作站、节目编排工作站等;(2)传输网络,利用现有的HFC网络巨大的频带资源实现数据传输;(3)用户终端,用户利用机顶盒或者Cable-Modem接收和浏览信息。

从图1可以看到,在DVB-C数字广播系统中,一个通道上传输的数据可能包含多路节目或来自多个节目源,因此需要对多路多节目TS流(MPTS)进行复合转接,生成一个符合DVB-C标准的MPTS,再经调制后在一个通道上传输。由TS复接器来完成这个功能。TS复接器在前端系统中相当于一个交换机,它负责对多个MPTS进行转换和复合,生成一个MPTS。在复合过程中,要完成包标识符(PID)过滤、PID重新标识、插入节目特定信息/服务信息(PSI/SI)、多路MPTS的交织等工作[4,5]。从中可以看出复接器在整个系统中的重要性,TS复接器工作是否稳定可靠,直接影响整个系统的正常运作。

2 TS复接器的设计方法

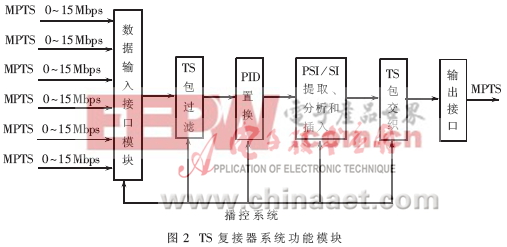

在该系统中需要对6路数字卫星电视节目进行复接。各路有效速率为0~15Mbps的异步串行接口(ASI)输入,6路总速率不超过36Mbps,输出为恒定速率38.1Mbps的ASI输出,输出的MPTS为符合DVB-C标准的传送流;复接器调整PID,包括将输入MPTS中的PSI/SI等不需要的信息过滤掉以及对有效TS包重新分配PID。新的PSI/SI信息作为复接器的输入按一定速率插入到MPTS中,插入的PSI/SI信息包括节目关联表(PAT)、节目映射表(PMT)、网络信息表(NIT)、服务描述表(SDT)等[4,5],复接器还能接受来自播控系统的数据信息,作为复接器输出流的一部分。系统的功能模块结构如图2所示。

由图2可以看到,由于需要处理的数据速率快、数据量大、要求实时性,一般的处理芯片无法完成。为了达到上述目的,采用高速DSP和FPGA一起来完成。整个系统基于DSP和FPGA,配以CPLD、高速SRAM、异步FIFO等。DSP具有运算速度快、计算能力强、可用资源比较丰富的特点,尤其适合于实现各种数字信号的处理功能,在各种领域具有广泛的应用。但由于所要处理的数据量太大,仅靠DSP片内RAM是远远不够的,所以还必须要有大容量、访问速度快的缓冲区对接收到的数据进行缓冲,以便于DSP进行处理。基本思想是FPGA完成TS包过滤和PID置换、PSI/SI提取等工作,系统的控制工作、TS包交织算法则由DSP完成,整个控制逻辑则由CPLD完成。

3 TS复接器的一种实现方案

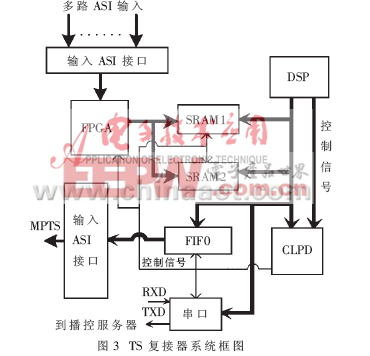

针对上述分析,采用DSP与FPGA相结合的方法成功实现了TS复接器,该实现方案如图3所示。图3中的DSP采用TI公司的TMS320VC5410-100,它具有100MIPS的快速处理能力,以及片内64K的RAM和多个串口等资源,其片外寻址空间可以多达8M Word。FPGA则采用了Xilinx公司的XCV300。

笔者为DSP扩展了2M Word的高速SRAM作缓冲,分为两个1M Word的双缓冲,处理时以帧为单位,DSP和FPGA只能访问其中一个1M Word的SRAM。一般情况下,FPGA从输入接口把一帧数据存入其中一个缓冲区,DSP对另外一个缓冲区进行操作,根据交织表把数据送到FIFO,再输出到输出接口,两者的总线切换由FPGA负责完成。

图3可以分为以下几个模块:

a.输入模块:使用ASI接口将270M串行编码数据转换成27M并行数据,并提供接收时钟、数据有效等控制信号。

b.FPGA模块:接收ASI接口输出的并行数据,实现同步、PID置换、PSI/SI提取等,并将数据写入SRAM中,跟踪记录每路的TS包数;产生帧切换脉冲,控制双缓冲区的切换。

c.DSP主控模块:DSP完成整个系统的控制功能,计算交织表,负责与播控系统的通信等。

d.CPLD模块:根据DSP提供的地址和数据进行译码,对总线上的各设备进行互斥片选;产生中断申请信号;对发送FIFO的全空信号进行采样,控制从发送FIFO读

实现 设计 宽带 DVB-C数据广播 TS复接器 DSP FPGA 网络 相关文章:

- 基于光纤到户技术实现智能小区三网融合(05-14)

- 基于DDC和DUC的大带宽DRFM设计与实现(04-24)

- 电子引信检测设备实现通用化应用(04-17)

- 融合是实现新一代门禁及电脑桌面登录安全性的关键(02-26)

- 基于基站定位和 GPS 的双定位跟踪系统架构和实现(12-19)

- 利用RF预失真实现功放线性化(12-14)