可重构平台下AES算法的流水线性能优化

时间:07-08

来源:互联网

点击:

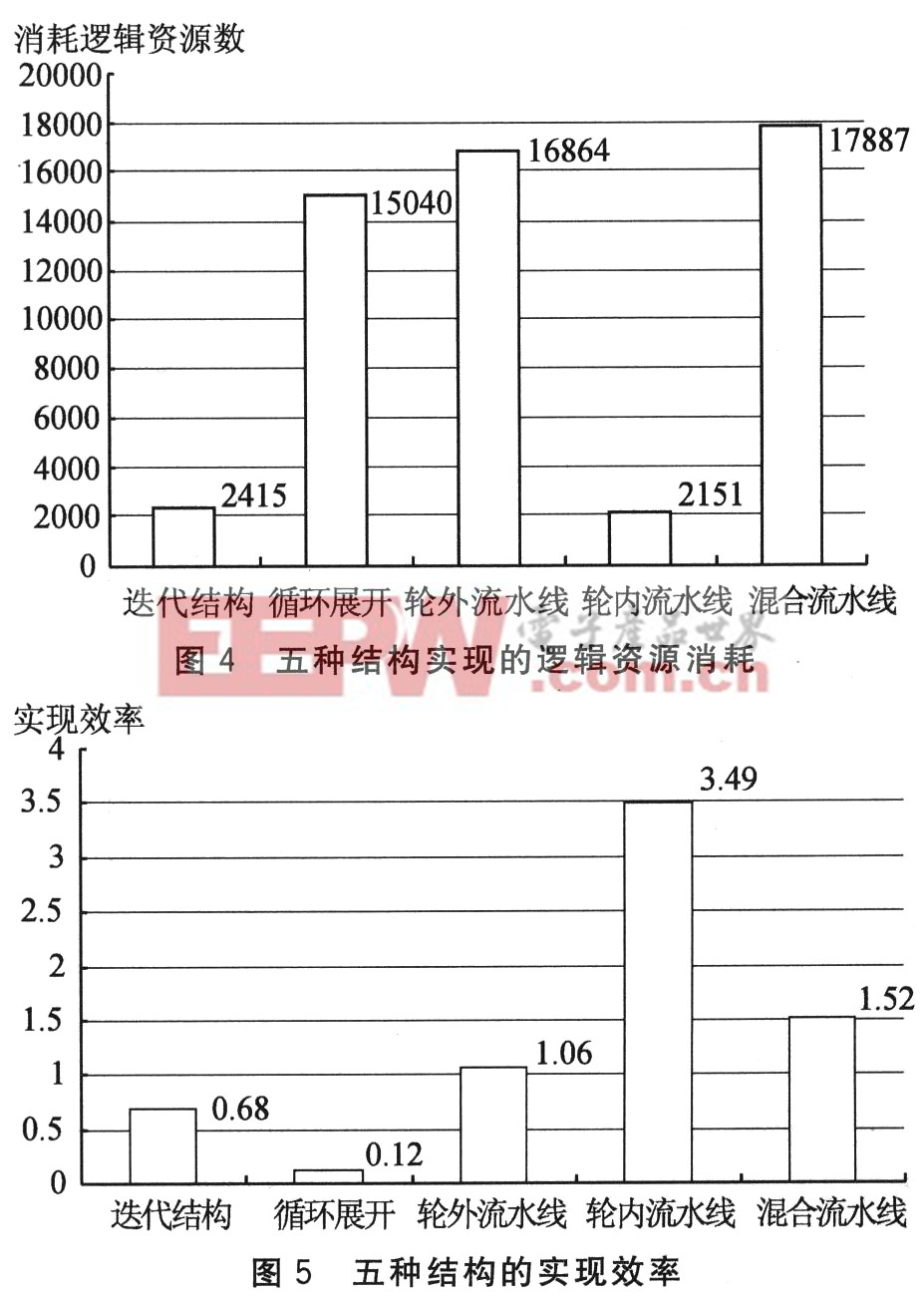

轮内流水线和轮外流水线结合使用,设计了混和轮内外流水线结构。混合轮内外流水线结构具有极短的流水线单级延迟,因而时钟频率可以提高到212.5 MHz。同时,混合轮内外流水线结构能够在每一时钟周期内完成一个数据分组的加密,这样,加密的速度就可以达到27.1 Gb/s。这一速度是目前有关AES的高速加密芯片实现的报告中数据较高的。为了达到这样高的加密速度,所需要的资源也是相当可观的。逻辑综合结果显示,完成这一设计需要17 887个逻辑单元,如图4所示。这相当于4块Xilinx XC2V1000 FPGA的容量。同时,我们也评估了各种实现结构的效率,用速率资源比,即每秒所能进行加密的Mb数除以设计所需的逻辑单元数目得到的比值作为结构的效率。从图5可以看到,轮内循环结构是最高效的一种设计,其比值为3.49;而循环展开结构效率最低,仅0.12。因此,在逻辑资源相对有限的条件下,选择使用轮内循环是比较合适的。

3 结 论

综上所述,除对AES加密算法基本运算变换的优化外,算法的整体实现结构对其加密性能的影响是很重要的一个方面。一般情况下,在对效率要求不是很高的环境中,迭代结构实现简单,所需资源最少,因而较为合适;但要达到更高的加密效率,并且希望实现代价较低的情况下,采用轮内流水线结构是一个较为合理的折中方案;只有当有大量资源可用并且追求最高的加密性能时,才有必要采用轮内轮间多级混合流水线结构。

- 高性能RFIC应对下一代射频系统设计挑战(05-04)

- 排除F频段组网障碍 提升LTE整体性能(04-23)

- RF MEMS实现LTE手机天线性能突破(07-17)

- RFID分形天线性能最佳(08-13)

- 详解什么造成手机的信号强弱(08-27)

- ZigBee系统结构与射频性能分析及射频测试方法(09-29)