一种基于FPGA和SC16C554实现多串口通信的方法

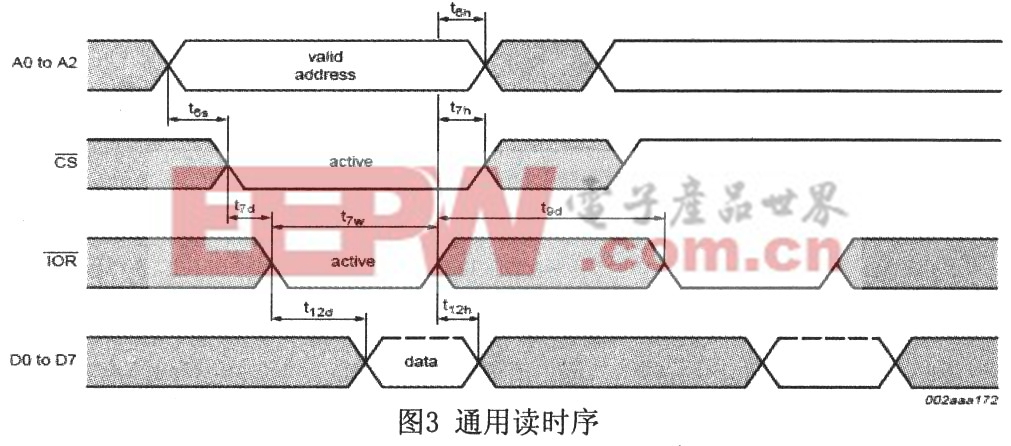

其中t6s=0ns t6h=0ns t7h=0ns t7d=10ns t7w=26nst9d=20ns t12h=15ns都为最小值,t12d max=26ns由图3可以看出:对串口进行一次读操作所需的时间T=t6s+t7d+t7w+t9d所以T最小为56ns。本设计采用60MHz时钟分频出10MHz时钟,在一个1OMHz时钟周期(100ns)内完成一次读操作。用6 0 MH z时钟同步一个计数器cscount[2:0],在第一个6 0MH z时钟的上升沿(cs_count=3’b000时)置CS为低,并赋对应的地址给UART A;在第二个60MHz时钟的上升沿(cs_cout=3’b001时)置UART IOR为低;在第四个60MHz时钟的上升沿(cs_count=3’b011时)置CS、UART IOR为高。这样UART IOR有效时间为两个时钟周期(33ns),且比CS延时一个时钟周期(17ns),完全满足图3读时序的要求。

由图2可知,由空闲状态State0到完成一次串口数据的读取,共需要500ns的时间。这样多通道工作时连续完成四个通道的读数操作共需2μs,远小于单个通道连续两个中断产生的时间间隔65μs;这样有效解决了多通道工作时,当读取数据的过程中其它通道中断丢失的问题。如:当读通道A数据的过程中,通道B产生中断请求;则状态机完成通道A数据读取返回到空闲状态State0,检测到INTB为高,状态机进入下一个状态(State5)进行通道B的数据接收。

4 测试结果及分析

我们分别对两种方案进行了测试,结果如下:表2为完全基于DSP接收和发送数据的通信性能测试;表3为基于FPGA接收串口数据的通信性能测试。

波特率发送周期数据长度测试结果

比较两种方案的测试结果可以得出以下结论:

1单通道工作时:两种方案的通信性能是一样的。

2多通道同时工作时:由表2测试结果可以看出,每次发送的数据量过大、或发送周期较小时,由于DSP对串口芯片中断请求的处理速度问题就会造成数据丢失。由表3测试结果可以看出,四通道工作时,发送数据长度为64字节,通道发送周期最小可达10ms;如果发送数据长度减小,通道发送周期还可以更小。该设计性能远远好于方案改进前完全基于DSP接收和发送数据的性能;能满足系统实际工作的需要。

5 结束语

基于FPGA接收数据的设计有两个突出的优点:1、极大提高了对串口中断的响应速度,避免了多通道工作、完全基于DSP接收和发送数据时数据大量丢失的情况;2、完全可编程设置DSP中断产生条件,解决了原来串口芯片只有1、4、8、14字节四个触发深度的限制,可编程设置存储空间范围内的任意字节的触发深度,大大减少了DSP的中断数量,提高了DSP的工作效率。另外程序具有较强的可移植性,当设计需要修改时,只需修改少量代码,有效降低了设计周期。

通信 方法 串口 实现 FPGA SC16C554 基于 收发器 相关文章:

- 无线通信领域中的模拟技术发展趋势(蜂窝基站)(09-22)

- 新一代移动通信系统及无线传输关键技术(06-19)

- 蜂窝移动通信基站电磁辐射对人体影响的探讨(04-10)

- 无线升级到802.11n 应考虑的因素有哪些?(10-30)

- 第四代移动通信系统中的多天线技术(08-05)

- 4G移动通信系统研究进展与关键技术(12-24)