DS/FH混合扩频接收机解扩及同步技术的FPGA实现

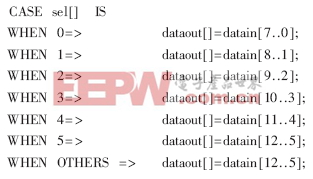

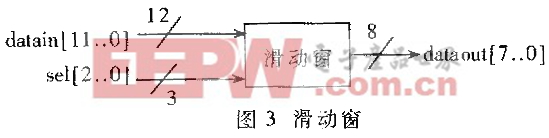

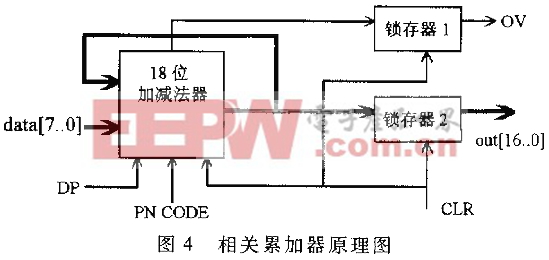

决定,结构如图3所示。滑动窗控制逻辑关系为: 符号扩展是为了与后面的相关累加器数据宽度保持一致,符号位扩展时需与输入数据最高位的符号保持一致。 1.3 相关累加器 相关累加器完成本地伪码与接收信号的相关累加运算,运算得到的结果送入DSP完成伪码的捕获和跟踪。取伪码长度为256位,采用半码片滑动,则一个码周期完成512次累加运算。如采用串行滑动相关捕获方式,则遍历所有的码相位所需要的时间为512个码周期,即捕获所需要的最长时间为512个PN码周期。由于可编程逻辑器件的发展,使得有足够的硬件资源来完成并行运算。此处采用串/并混合的捕获方式[6][7],采用8路相关累加器,每一路分为超前、当前、滞后3组,每组相差半个码片的相位,每一路相差64个半码片的相位。这样,只需滑动64个半码片相位就可以遍历所有的伪码相位,完成捕获所需时间缩短为原来的八分之一。数据解调由另外4组相关累加器完成。由于发射端同步伪码与数据伪码相位严格对齐,所以在接收模块中,完成同步伪码捕获跟踪后,直接将所获得的相位信息用于数据解调相关器,即可正确解调数据。 同步伪码的跟踪采用超前―滞后延迟锁相环路(DPLL),每一路相关器包括3组累加器。捕获跟踪及数据解调共使用28组相关累加器,每一组相关累加器结构都是完全一样的,均分为I、Q两路,分别进行累加运算,完成512次累加运算后由DSP读取数据。I、Q两路结构完全相同,其中一路的原理图如图4所示。 相关累加器由18位加减法器、锁存器1和锁存器2组成,data[7..0]为下变频后的输入数据,PN CODE来自码发生器。作为控制端,低电平完成加运算,高电平完成减运算,DP上升沿进行数据锁存,下降沿完成一次累加运算。当累加运算完成后,由CLR信号清零并将结果存入锁存器2,CLR下降沿有效。锁存器1输出OV信号作为溢出标志位,锁存器2输出累加结果out[16..0]。输入与输出端的最高位为符号位。 1.4 本地码发生器及码移相电路 本地码发生器用于产生本地PN码,从而与接收信号进行相关运算。由于发送端采用编码扩频调制方式,接收信号中既有同步PN码,还有数据PN码,与接收信号相对应,本地也应该产生相应的PN码,用于同步及解调数据。 本地PN码发生器全部采用FPGA实现,并且设置了可编程寄存器和外部接口,DSP通过接口可预置PN码长度。1024进制计数器电路用于产生ROM的输入地址,ROM由FPGA内部RAM资源来实现,采用ALTERA公司APEX20K200器件。该器件内部可编程RAM容量为106496位,完全可以满足设计需求。本地PN码采用半码片滑动方式,ROM内部PN码也以半码片方式存储。如码长为256,采用半码片存储方式后,每一组PN码需存储512位数据,相应的ROM有9位地址线驱动输出。驱动时钟为PN码时钟的2倍。在实际设计时,PN码发生器内存放了8组PN码,但只用了五组,一组用于同步,另外四组用于解调数据。ROM输入地址由1024进制计数器产生,实际上只需用512进制计数器即可得到ROM输入地址。考虑到可扩展性,这里采用了计数容量最大为1024的可变计数器。由DSP通过DSP-FPGA接口改写寄存器值,可以很方便地调整PN码的输出相位。 伪码移位电路的主要作用是将码发生器产生的PN码进行移位操作,从而得到伪码的不同相位。捕获和跟踪过程共使用了8路24组相关累加器,每一路分为超前、当前、滞后3组,这3组累加器输入端PN码相差半个码片的相位,8路相关累加器中每相邻两路相差64个半码片。码发生器输出5组PN码序列(第0组~第4组),分别对应同步伪码及4组数据伪码。5组伪码均经过512级移位寄存器,第0组PN码作为同步码,取其0、1、2相位作为第一路的超前、当前、滞后3组相关累加器的输入;64、65、66相位作为第二路的超前、当前、滞后3组相关累加器的输入,其余各路依此类推。当完成捕获后,需要将捕获所得的同步PN相位切换到数据解调相关累加器中。例如,假设在第二组相关累加器的当前通道捕获,那么此时解调数据用的相关累加器的PN码相位就应该与第二组相关累加器当前通道的PN码相位保持一致。数据伪码相位切换的实现是由DSP记忆捕获通道的相位,然后控制多路选择开关选择该相位。 2 同步模块的FPGA实现 同步模块由位同步及帧同步电路构成,主要实现对信息数据的检测和提取,并识别一帧信息数据的帧头位置,实现跳频图案的同步。跳频图案的同步采用等待搜索同步法,开始时接收端频率合成器停留在某一单频点fi′,等待发射机的频率fi,当发射机的频率跳变为fi时,接收端本地的频率fi′与发送的频率fi混频后,输出中频fIF。DSP完成解扩解调运算后,得到的串行数据流送入位同步和帧同步电路,从数据流中提取出特征字,就可以获得一帧完整的数据,从而确定帧头的位置,即频率转换时刻,由此控制接收端频率合成器与发送端频率合成器同步跳变,实现跳频图案的同步。由于采用编码扩频调制方式,发送端每两位信息比特在一个PN码周期被编码为4种PN码中的一种。所以接收端在每一个PN码周期,对4组数据相关累加器的累加结果进行最大值比较,然后译码成相应的信息数据。信息数据送到同步电路,进行巴克码匹配相关,提取有效的信息位,并控制跳频时序完成跳频同步。同步模块原理如图5所示。

技术 FPGA 实现 同步 扩及 混合 扩频 接收机 DS FH 转换器 相关文章:

- 基于Zigbee技术家用无线网络的构架(12-14)

- 无线通信领域中的模拟技术发展趋势(蜂窝基站)(09-22)

- 第四代移动通信系统中的多天线技术(08-05)

- 移动WiMAX 802.16 Wave2的技术特点(02-04)

- Wi-Fi的最新技术进展及未来应用方向(03-16)

- UWB超宽带传输技术及其应用简析(03-18)