基于一个多路计时系统的设计方案

摘要:本文介绍了一个多路计时系统的设计方案,给出硬件电路,重点阐述了高精密计时系统的设计方法。并说明了系统采用可*编程芯片的设计技术。

1.前言

各种微机接口电路应用中,需要精密计时器,特别是多路精密计时器,可广泛应用于仪器仪表中。例如:目前国内各级学校在体育教学及举行跑步比赛时,计时采用手动按秒表的方式进行,这不可避免地出现计时不准以及出现错误的结果的情况。精密多路计时器则可用于这种系统中。

2.硬件系统方案

在多路计时器用于跑步计时时,需要一个起动计时信号,由发令枪产生;八个计时停止信号由运动员到达终点产生。

2.1 硬件系统框图

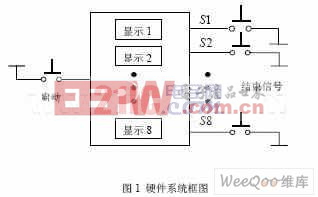

图一为硬件系统框图。

图1中系统由个人计算机加硬件接口构成,因此整个系统的设计为硬件接口与软件系统设计。当得到启动信号后,8个计时器开始工作,显示器实时显示8 路计时器值。S1~S8代表8路结束信号。

2.2 核心电路方案

核心电路采用8253计数定时芯片技术。图2为示意图。

图2 给出了八路计时器中一路的原理电路,每路采用8253芯片中的两个计数器。 图中D触发器用于计数器的启停。当gate为高电平计时器计时,当gate为低电平计时器停止计时。

3.系统计时工作分析

以该系统用于短跑计时分析,系统可用于100米、200米和400米三种情况。下面主要以用于100米情况进行分析。

3.1 计时器工作方式的选定

计时精度取1/200秒,设完成100米跑步计时间最长为30秒,此时计时器1采用工作方式2,BCD码计数,系统时针信号取1MHZ,计数值取5000,因此其输出信号为200HZ,其确定了计时精度为1/200秒。

计时器2采用工作方式2,BCD码计数,计数值取6000。

同样的分析,当为200米计时时,设完成200米跑步计时间为60秒,计时器1采用工作方式2,BCD码计数,系统时针信号取1MHZ,计数值取5000,计时器2采用工作方式2,进制计数,计数值取12000。

当为400米计时时,设完成400米跑步计时间为120秒,计时器1采用工作方式2,BCD码计数,系统时针信号取1MHZ,计数值取5000,计时器2采用工作方式2,进制计数,计数值取24000。

3.2 时间的计算

工作中计算时间时,主要读取计时器2 的值,以用于100米情况进行分析,设读取值为X,则计时时间T为:

3.3 基于PCI的接口设计

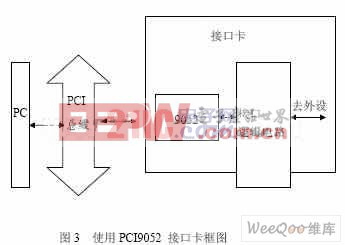

利用PCI9052设计PCI总线的接口电路非常简便 ,在使用PCI9052开发板时可采用两种方案验证:(1)利用开发板的ISA总线接口,设计在我们早已熟悉的ISA总线上进行;(2)在开发板的预留区引用PC9052提供的总线进行设计。图3是我们设计的采用PCI总线的多路定时器。

PCI总线上的主机CPU可通过PCI9052直接读取I/O状态与数据。

4.软件设计

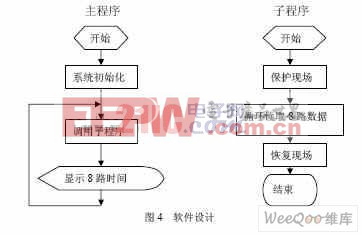

程序设计分为主程序与子程序两部分。主程序用于系统硬件的初始化,显示多路计时状态。子程序用于读取计时器的值,并送出显示,框图见下:

5.系统的实现

5.1 用于跑步计时输入电路的设计

在多路定时系统用于跑步计时,存在跑步终止信号正确识别问题。我们在每个跑道的终点处,上下设置5路红外线检测装置,为了确保无能运动员胸部以上部位到达终点为有效到达,因此要求5路信号中,有两路以上信号有效时才产生跑步终止信号。

5.2 用可编程芯片实现接口电路

用FPGA(Field Programmable Gate Array )芯片实现上述电路具有可靠性高,电路简单的特点。在实现跑步计时系统的输入电路时,每一跑道至少具有5个信号,8个跑道共有40个以上的输入信号,因此采用可编程芯片可大大减少芯片的数量。而核心计时电路采用3片8253芯片,为减少芯片数量,我们采用可编程芯片实现。

图5为计时器部分信号仿真结果,其中NX1为时钟信号,TLA、THA为计时器的低6位及高8位,RAMDI为定时器初值。

6. 结论

用可编程芯片加PCI接口芯片设计多路精密定时系统,在实际工作中具有广泛的实际意义。用于跑步计时器中,尚需考虑启动信号与结束信号问题,特别是结束信号处理问题。

- 直接变频接收机设计可实现多标准/多频带运行(10-11)

- 基于蓝牙芯片的无线通信模块设计与开发(02-03)

- 无线通信网络设计与现场测试(10-10)

- WiMAX数据传输加密方案设计与实现(05-25)

- 高性能TD-SCDMA接收机的设计(03-15)

- 初步设计WiMAX射频系统(03-29)