嵌入式编程需注意的Cache机制及其原理

1 Cache的原理

Cache即高速缓存,它的出现基于两种因素:一、CPU的速度和性能提高很快,而主存速度较低且价格高;二、程序执行的局部性特点。将速度较快而容量有限的SRAM构成Cache,可以尽可能发挥CPU的高速度。CPU与外设交换数据时经常用到buffer(缓冲),这与缓存极其相似,只不过Cache是为了提高CPU和内存之间的数据交换速度而设计,而buffer是为了提高内存和硬盘(或其他I/O设备)之间的数据交换速度而设计的。

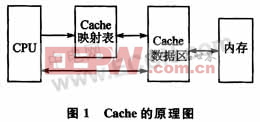

Baidu快照(cache.baidu.com)就是一个缓存的例子,其作用与计算机CPU缓存有类似之处。 Cache的原理如图1所示。

在读取内存数据的同时CPU将数据保存到Cache数据区,同时更新Cache映射表(保存地址信息,表示该地址的数据是否已在Cache数据区,即是否命中)。这样,CPU再次读取该地址数据时,就可以直接从Cache提取。读Cache的时间远小于直接读内存,可提高CPU读取数据的效率。

Cache数据区有成块读取的特性(Cache映射表保存的地址是块地址,节省空间,也符合程序执行的局部性特点)。Cache数据区远远小于内存空间,就需要相应的替代算法。比如最近最少使用算法,可将新数据替代使用频率低的数据,同时更新映射表信息。可以推想,Cache空间越大,命中率越高。

写内存需要直接更新内存。如果映射表存在该地址信息,还需要同时更新Cache数据区。这种Cache访问方式就称作“直写”,Samsung公司的ARM7微处理器S3CA510B就是这种方式。以下所讨论的Cache问题除非特殊说明,否则都是“直写”方式。

2 嵌入式编程时需注意的问题

2.1访问外设使用Cache的问题

在访问内存时使用Cache是不会出现问题的,但如果访问数据易变外设(数据不依赖于CPU写操作而改变)时使用Cache就可能出现问题。问题在于外设数据的改变不仅仅依靠CPU写操作,CPU第一次读取外设数据时将外设的数据和地址信息保存到Cache,第二次读取外设数据时就可能有问题出现。这是因为数据直接从Cache提取,而外设的数据可能有改变。

因此,在访问易变外设时要禁止使能Cache,直接读取外设数据到CPU,而不经过Cache的任何环节,即保证不改变Cache映射表和Cache数据区内容。

S3C4510B的SYSCFG SFR(特殊功能寄存器)有用来控制Cache使能或不使能的,通过对该SFR的设置可暂时禁止Cache或重新恢复Cache功能。这样就可以在读取外设前禁止Cache,读取结束后重新使能Cache,保证了外设数据读取的正确性。写数据到外设时采用“直写”方式,更没有问题。

2.2开关Cache引发的新问题

在Cache开关期间,如果有另一个进程/任务访问内存,在此期间写内存并且该内存在Cache中已有映射(注意,它也是被禁止Cache的,所以它不会同时更新Cache数据区的内容),那么在Cache重新使能之后Cache数据区的信息已经过时了,而Cache映射表还是Cache禁止之前的状态,如果CPU此时读数据就会得到过时的数据。这样看来,引发的问题范围更广了,连内存的数据读写正确性都无法保证。与内存泄漏的影响来比较,内存泄漏如果是一颗定时炸弹,那么Cache问题就可以说是随时随地都可能踩上的雷区,因为程序一旦开始就可能引发爆炸。

如图2所示,Cache使能时Cache映射表和Cache数据区保存了内存的数据信息,这是CPU访问内存时通过图中实线箭头通路实现的。内存的信息可以与Cache的信息保持一致。

Cache禁止时的情况有所变化。由图2中虚线箭头通路直接进行内存访问,且地址0x00处的数据由55变为AA,但Cache区的信息仍为之前的状态。很明显,Cache的数据是应该废弃的,但是Cache映射表仍保存0x00的地址信息。Cache重新使能后,CPU再次读取0x00地址的数据,由于Cache仍是命中,直接从Cache数据区中提取数据,这样读出来的数据就是0x55了。

由S3C4510B数据手册第4节的第21页可知:通过对SYSCFG寄存器的CE位置1或清0可使能/关闭Cache,但是Cache没有内容自动刷新功能,在重新使能Cache时需考虑Cache数据的正确性。

为了证实以上说法,循环执行如下测试程序:

如果没有Cache的影响,结果应该是55 aa aa。可见,Cache关闭再打开的确可造成Cache数据过时。

3其他CPU解决方案

Atmel公司的AT91RM9200和Samsung公司的S3C44B0,用这两种CPU先后移植过操作系统,且在对外设访问的整个过程中Cache都是使能的。它们的解决方案是什么呢?

AT91RM9200是ARM9系列带有MMU的CPU。MMU对内存有分页管理功能,可以实现多个进程的内存空间保护。Cache是通过MMU管理的,这也是Cache和MMU经常同时存在的原因。

S3C44B0和S3C4510B同样都是Samsung公司产品,并且都不带MMU。与S3CA510不同的是,S3C4480自带的SFR可以配置非缓存范围,即使Cache使能,所设置范围的地址空间访问也不通过Cache实现。这样,可以很方便地实现内存是缓存区,其他外设是非缓存区。

这两种方案对于S3C4510B都无法实现。网络上有人用volatile关键字解决外设访问问题。volatile关键字是在源代码中给编译器看的,它可能影响编译器的编译结果,但是最终CPU执行都体现到汇编语句,如果汇编语句都不能解决Cache问题,volatile语句也是不可能解决的。

对于易变数据的外设使用volatile关键字是应该的,可避免编译器的优化,比如以下语句:

在两次读取portAdd地址的数据相同时等待,可以用到等待信号跳变的程序。如果将volatile关键字去除,有可能经编译器优化,Value2不会从实际的portAdd地址读取数据,而是利用Valuel读取语句的中间寄存器直接获得。

4 本文解决方案

由S3C4510B手册上第5节的第4页可知,可以通过两种方式保证Cache数据的正确:

①对Cache映射表的Tag RAM数据清零。Cache映射表数据一般是通过上电复位清零的,如果Cache或内存段的设置被修改,则会造成Cache映射表数据废弃,这时就需要通过程序对Cache映射表数据清0。

②S3C4510B提供非Cache方式访问控制位,控制位ADDR[26](地址线26位)为“1”时,按非Cache方式访问。因此,Cache使能的情况下,地址0x000 0000~0x3FFFFFF按Cache方式访问,而0x400 0000~0x7FF FFFF按非Cache方式访问。实际上,0x000 0000+offset与0x400 0000+offset(offset在0x000 0000~0X3FF FFFF之间)是同一地址,不同的是Cache是否起作用。

可以得到两种解决方案:

(1)Cache映射表手动更新 既然在开关Cache之后内容过时,并且CPU不会自动刷新,可以通过手动更新的办法来抛弃废旧信息。也就是说,将Tag RAM区(前面所说的Cache映射表)清除,这样所有Cache数据区的内容都不使能,再次读取数据时同时更新Cache映射表和Cache数据区内容,之后才能使用。清除操作将Tag RAM的1 KB内容清零,需要消耗一定时间;并且这样操作后Cache是0命中率的,只有一定访问次数后Cache信息重新填满,才能恢复正常的命中率。因此,频繁地开关Cache时采用这种方案是不可取的。

(2)bit26位控制Cache使能

S3C4510B的地址线为26位(bit0~bit25),实际上CPU可访问空间为32位(bit0~bit31)。一般我们都不使用bit26~bit31,不过S3C4510B的这些位有着特殊的控制功能。通过bit26的高电平可以禁止该地址的Cache功能,因此将外设的地址由原来的ADDR_PORT改为(ADDR PORTO(126)),就可以实现外设访问时Cache不使能。这样就不用改为SYSCFG的Cache使能控制位。比较来看,SYSCFG的Cache使能位是控制整个CPU访问的Cache使能与否,而bit26只控制当前访问的一个具体地址的Cache使能与否。采用这种解决方案理论上有依据,并且可以最大程度发挥CPU的功能。

5 修改程序后的试验结果

修改Cache解决方案后,可以解决内存访问错误的问题。经过测试,采用“bit26位控制Cache使能”的方案可以顺利访问外设,代码执行始终是在Cache使能的情况下,并且不影响内存数据。若完全关闭Cache的程序,执行同样代码需要花费5~8倍的时间。

及其 原理 机制 Cache 编程 注意 嵌入式 相关文章:

- NAP技术和NAC技术之间的比较及其分析(01-30)

- 连续超声波位置跟踪器的设计原理及其应用实现(11-04)

- 拒绝繁琐 智能布线前沿技术及其应用(10-30)

- 无线自组网技术VBee简介及其应用实例(10-07)

- 无线自组网技术VBee及其应用实例介绍(09-19)

- MPLS技术及其在城域网中的应用(09-01)