基于NlOSII处理器的IEEE-1394 b双向数据传输系统

摘要:基于FPGA内嵌的NIOSII处理器,设计了一个1394b双向数据传输系统。介绍了该系统的硬件结构,描述了其软件工作流程,主要包括异步传输和等时传输的具体实现过程。测试结果表明,该系统的传输速率较高、可靠性和实时性较好,并具有一定的应用价值。

关键词:1394b;NIOSII;等时传输;异步传输

随着IEEE Std 1394-1995技术的高速发展,IEEE 1394已经成为众多电子设备基本的外部接口。然而,要进一步扩展它的适用领域,就必须克服其接口被限制工作在较短距离以及不适用于较高数据传输率的缺陷。IEEE Std 1394b-2002作为其修订版本支持800 Mb·s-1传输速率,且中继距离长达100m。它将原来的DS(Data-Strobe)编码方式改进为8B/10B编码方式,这对于1394性能的改进起着决定性作用。同时,1394b是向下兼容的,也就是说同一个电路既可以选择使用DS编码也可以选择使用8B/10B编码。

现在符合1394b标准的链路层和物理层控制芯片都遵循1394 OHCI(开放式主机控制接口协议),它的主要功能是实现总线的链路层协议。本系统通过NIOSII处理器,根据1394 OHCI,对FPGA以及1394套片进行控制,实现了双向数据传输。其主要功能是将外部视频数据打包,按照1394b协议,传输到主机端进行实时显示,并实现与主机的相互通信。

1 1394 OHCI的特点

支持事务层和总线管理层,而且带有一个PCI主机总线接口,以及高速率数据传输所需要的DMA引擎。支持两种数据传输:异步传输和等时传输。

异步传输:1394 OHCI可以发送和接收所有1394所定义的数据包格式。无论是从主机存储器中读出发送数据包,还是将接收到的数据包写入主机存储器,都是通过DMA来实现的。在向主机总线存储空间读和写时,1394 OHCI也可以通过直接执行1394读和写请求而作为主机总线和1394之间的总线桥。

等时传输:1394 OHCI可以执行循环控制器的功能。也就是说它包含了一个循环计时器和计数器,可以在8 kHz时钟的每个上升沿后安排一个循环开始包的传输。1394 OHCI可以产生内部时钟。当它不是循环控制器时,1394 OHCI根据循环开始包,通过更正其循环计时器来保持它的内部时钟与主节点的周期同步。1394 OHCI为等时发送和等时接收各提供了一个DMA控制器。每个DMA控制器支持高达32个不同的DMA上下文(context)。等时发送DMA控制器可以在每个周期,从每个上下文发送数据。而每个上下文只能从唯一的等时信道发送数据。等时接收DMA控制器可以在每个周期,从每个上下文接收数据。但是每个上下文既可以从唯一的等时信道接收数据,也可以从多个等时信道接收数据。

2 硬件结构

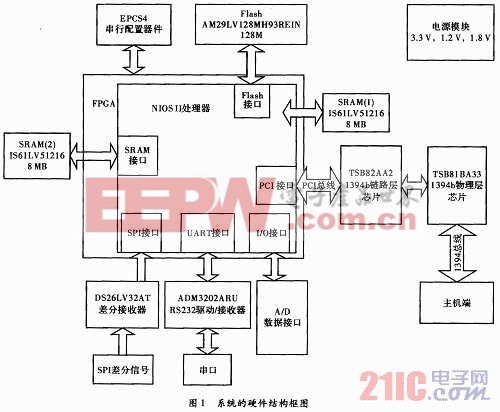

以FPGA内嵌的NIOSII处理器为开发平台,控制实现数据的双向传输。其硬件结构框图如图1所示。主要由NIOSII系统模块、SPI口的数据输入输出模块、1394套片模块、SRAM模块、串口(UART)通信模块、电源管理模块、EPCS模块和Flash模块组成。其中,FPGA芯片为主控芯片,选择Ahera公司Cyclone II系列的EP2C70F672C8N;Flash芯片用于存储NIOSII嵌入式处理器的代码和数据,FPGA上电后从中读取;SRAM芯片一个用于对外部大量视频数据进行缓存,另一个作为C代码的运行空间。串口主要用以产生异步数据,外部视频数据则主要通过SPI口进行等时传输。

3 软件工作流程

在NIOSII IDE集成环境下,根据1394 OHCI协议,使NIOSII处理器实现对总线的初始化,以及管理,并通过DMA方式实现等时和异步数据传输。其中等时数据传输仅考虑将外部视频数据打包发送到主机,而异步数据传输分为主机发起的异步传输和1394设备发起的异步传输。

3.1 系统的自举

主要为系统初始化、检测电缆以及根节点的确定。系统初始化主要是配置链路层芯片寄存器,使其工作在需要的状态下。分为对PCI寄存器的初始化和对OHCI寄存器的初始化。对PCI寄存器的初始化包括对TSB82AA2设备ID和PCI厂商ID的验证,OHCI基地址寄存器的设置以及对指令状态寄存器的配置。而对OHCI寄存器的初始化则包括对各个中断寄存器和DMA上下文的设置,以及控制寄存器的配置。检测电缆是否插入是通过读取物理层芯片某寄存器的相应位来判断的。电缆插入后,通过检查和配置Node ID寄存器,强制设置本节点为子节点,主机为根节

点,直到成功为止。

3.2 数据的传输

在1394 OHCI中,不管是等时传输,还是异步传输,都是通过DMA方式实现的,而且每个DMA都有一个FIFO,用于暂时存放数据。其中各FIFO的存储容量为:异步发送(AT)FIFO为5 kB,异步接收(AR)F7FO为2 kB,等时发送(IT)fIFO为2 kB,等时接收(IR)FIFO为2 kB。无论是物理层接收到的还是要发送出去的数据包,都被暂时存放在相应的FIFO中,由1394套片的内部逻辑控制将其传送到1394总线上。

(1)主机发起的异步传输。

主机发起的异步传输即由主机发出异步传输请求,1394设备进行响应,因此在这一部分,主要是异步请求包的接收以及异步响应包的发送。其工作流程如图2所示。1394设备接收到主机发来的异步请求包后,就会产生异步接收请求中断,这可由链路层芯片中断寄存器的RQPkt位表征。当一个数据包传送完毕后,数据包的最后一个指令描述符的xferStatus字段将被重置,这时数据包已被成功传送到AT响应FIFO中。

数据 传输系统 双向 IEEE-1394 NlOSII 处理器 基于 相关文章:

- 基于GPS的数据采集系统的研究(01-15)

- 带以太网接口的GSM无线数据传输系统设计与实现(10-06)

- 探讨如何应对未来移动数据业务的高速增长(03-17)

- 在多通道宽带射频系统中通过低压差分信号传输数据总线实现大型射频数据共享(03-24)

- 无线射频识别技术在规模化奶牛场的应用(05-14)

- 瑞风智能一卡通社区解决方案(05-15)