基于ZigBee技术的公共时钟系统构建

摘要:构建了一种基于ZigBee技术的公共时钟系统,依据ZigBee的不同技术,分别构建了它的总体结构、时钟同步算法以及软硬件结构。该公共时钟系统在某电站办公综合楼内经过一年的实验运行,结果表明系统时钟同步精度高,运行可靠稳定。

关键词:公共时钟;时钟同步;ZigBee;分布式网络

引言

在科学技术、社会生活和生产活动中,时间是个基本参量。随着科技的进步,许多公众场所聚集了大量的设备系统,这些系统必须依照统一的时间运行,才能保证整个公众场所的活动有序协调地进行。公共时钟系统功能就是为公众场所提供统一的标准时钟,它对公共场所活动的正常工作起着非常重要的作用。因此,公共时钟系统是一种重要的基础设备,已有越来越多的公众场所建立这样的公共时钟系统。

公共时钟系统是个分布式网络系统,标准时钟通过这个网络传递到公众场所各系统中。目前,人们已经利用局域网、CAN网和RS485网实现了公共时钟系统。这些公共时钟都是基于有线网络的,有其自身的缺陷,如需要事先规划布线、成本高、系统构建不灵活等。

随着无线传感器网络的发展,其非布线、自组织等优点,为公共时钟系统的实现提供了新的技术途径。目前无线技术有多种,如蓝牙、WiFi及WLAN等。相比它们,ZigBee技术具有传输距离远、成本低和组网性能好等优势,已经成为目前市场前景最广阔的无线通信与网络新技术之一。

本文以ZigBee技术为基础,构建了一种公共时钟系统:首先依照ZigBee的簇状拓扑结构及设备类型,构建了公共时钟系统总体结构;然后考虑到ZigBee传输的低速性,设计了一种精度高但简单的时钟同步算法;最后选择了一种ZigBee专用芯片,设计了系统的硬件结构,基于ZigBee协议栈,编制了系统软件。所设计的公共时钟系统在某电站办公综合楼经过了一年的实验运行,实验结果表明系统时钟同步精度高,运行稳定可靠。

1 系统总体设计

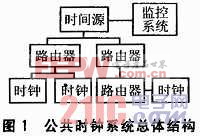

ZigBee技术具有网络自组织的特点,它支持星型结构、网状结构和簇状结构。星型结构网络覆盖地域有限,而网状结构网络复杂,实际中实现起来困难。因此,本文采用簇状结构结构来构建公共时钟系统,如图1所示。

系统中主要包括时钟源、中继路由器、时钟终端和监控系统。

时钟源:接收GPS标准时间;通过路由器向时钟发送标准时间;作为协调器组织网络,指定路径进行通信。

中继路由器:按同步算法接收标准时间,反馈本地时钟给监控系统,做信息的转发工作。

时钟终端:按同步算法接收标准时间,反馈本地时钟给监控系统,在LED显示屏上显示标准时间。

监控系统:负责接收、处理和管理接收来的同步系统状态数据,是台PC机。

公共时钟系统时间同步所有的任务都从协调器开始,在组网时每一个节点都只有一个父节点,协调器是最大的父节点,协调器通过建立一个节点信息库来管理整个网络。同步系统通过中继路由器将时间信息传递到时间源的广播范围之外,实现整个网络的时间同步。

可见,公共时钟系统遵循分层思想,所谓的一层,实际上是一个广播通信域,在该层之内的节点都在时间源或路由器的广播通信域之内,中心节点的层次号设为0。时间同步过程中,首先对网络中的节点进行分层并赋给每个节点一个层次号,然后在每一层中利用时间同步算法进行时间同步,最后形成全网时间同步。

2 同步算法设计

ZigBee技术具有低速率和大容量特点。因此,在设计公共时钟系统时,必须首先建立一个精简准确的时钟同步算法。本文给出的时钟同步算法如下:

①假设父节点与子节点的时间偏移量为△t;

②父节点记录t1时间戳,发送t1和△t编码给子节点;

③子节点记录接收到t1和△t编码,并启动一精确延迟定时器,此定时器计数间隔为a;

④子节点对t1和△t编码进行处理和验证;

⑤若t1和△t编码无误,则在定时器计数完毕后,再次启动一精确延迟定时器,定时器计数间隔为a。同时子节点根据(t1+△t+a)调整自己的本地时间;

⑥定时器计数再次完毕后,子节点记录当前时刻t3时间戳,向父节点回复t3和a编码;

⑦父节点记录接收到t3和a编码的时间戳t4;

⑧父节点按下式计算△t;

⑨在下一同步周期,返回②。

这种算法的优点为:计算简单,同步精度高,同步效率高,同步精度可以实时反馈给监控系统。因此,上述时钟同步算法适合低速、大容量的ZigBee网络应用。

3 硬软件设计

3.1 硬件设计

Chipcon公司的CC2420和CC2430是常见的ZigBee射频芯片,它们实现ZigBee协议的物理层和媒体访问控制器层具备65000个节点通道并可随时扩充,芯片的传输速率为250 kbps,具备CSMA-CA通道状态侦测,而且具有耗电低、唤醒时间快速等特性。

CC2430具有集成度高、体积小以及成本低等特点。芯片上整合了ZigBee射频(RF)前端、内存和微控制器。它使用1个8位具有增强型8051核的微控制器,具有128KB可编程闪存和8 KB的RAM,还包含模拟数字转换器、几个定时器、AES128协同处理器、看门狗定时器、32kHz晶振的休眠模式定时器、上电复位电路、掉电检测电路,以及21个可编程I/O引脚。

时间源节点兼顾协调器功能,需要较多的计算和存储资源,因此时间源节点采用CC2420和ARM的组成方案。因为路由和时钟节点只完成数据的转发,只实现简单功能的ZigBee协议栈,所以路由和时钟节点采用CC2430的组成方案。时间源节点、路由和时钟节点框图如图2所示。其中,时间源节点还包括GPS接收电路,用以接收GPS标准时间;时钟节点还有LED电路,采用74HC365作为驱动电路,用以驱动LED指示时间。

系统 构建 时钟 公共 ZigBee 技术 基于 相关文章:

- 第四代移动通信系统中的多天线技术(08-05)

- 透析信道效应对MIMO系统运作效能的影响(01-18)

- 如何发展中国第二代导航卫星系统(02-02)

- 北斗卫星导航系统的特点(02-02)

- 基于无线传送的智能家居室内通信系统(01-03)

- 基于WiMAX技术的5.8G无线专网射频系统设计(10-06)