应用于频率合成器的宽分频比CMOS可编程分频器设计

0 引言

高速、宽分频范围的可编程频率分频器设计一直是射频频率综合器设计中的难点,它的工作速度限制了频率合成器输出信号的最高频率,它的相位噪声影响频率合成器的带内相位噪声。文中设计的可编程分频器应用于移动数字电视接收机调谐芯片,该芯片兼容了DVB-H、DAB标准,接收的频段覆盖了460~900 MHz,1 400~1 500 MHz这两个频段。根据整个芯片的系统方案设计,可编程分频器的工作频率为2.4~4.0 GHz,实现的分频比范围为240~400,且为连续的。目前高速可编程分频器主要包括基于双模预分频的吞脉冲分频器和基于基本分频单元的多模分频器两种结构,前者因高速、结构简单等特点,被广泛应用在射频频率综合器当中,同时,整个可编程分频器单元模块都采用基于源极耦合(SCL)结构的模拟电路实现,相对于在低频分频部分采用数字标准单元具有噪声低、版图面积小等优点。检测和置数逻辑时序的设计是可编程分频器设计的重点,它直接影响到分频器的工作频率。本文中提出一种新的检测和置数逻辑及电路实现,使得整个可编程分频器的工作频率提高了1倍。本文首先给出r可编程分频器设计的整体结构,着重描述了可编程分频器检测和置数逻辑电路的改进方案;最后,给出了版图设计以及电路后仿真结果。

1 可编程分频器的结构

1.1 整体结构设计

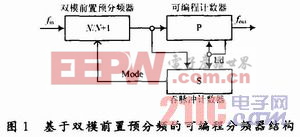

基于双模预分频器的可编程分频器结构如图1所示,它由3部分构成:N/N+1双模前置预分频器、可编程计数器、吞脉冲计数器。

输入的频率首先经过预分频器进行分频,分频比由吞脉冲计数器S给出一个信号Mode进行控制。可编程计数器P和吞脉冲计数器S同时开始减计数,当S计数器减计数减为0时,双模预分频器分频比由N+1变为N,S计数器停止计数,P计数器继续减计数;当P计数器减计数到0时,通过反馈回路使P,S计数器重新置数,开始新一轮的计数。因此在每一次计数过程中首先进行了S次N+1分频,再进行了P-S次N分频,故输出信号为:

分频比M=PN+S。

根据调谐器芯片系统所需要的频率合成范围及精度要求以及采用的TSMC 0.13/μm工艺,该设计将双模前置分频器设计为4/5双模分频器,P计数器为7位、S计数器为2位。因此该可编程分频器可实现的最大分频比为515。

1.2 4/5预分频器结构

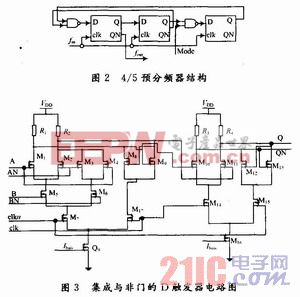

4/5预分频器采用同步计数结构,其结构如图2所示,由3个SCL结构的D触发器和两个与非门构成。Mode信号为分频比控制信号,当Mode为“1”时,预分频器分频比为5,当Mode为“0”时,预分频器分频比为4。由于4/5预分频器直接工作在VCO的输出频率下,是整个可编程分频器工作频率最高的部分,因此这部分的电路设计主要偏重于速度,其功耗是最高的。这部分电路采用SCL结构的模拟电路来实现,SCL结构的电路由开关管对尾电流的导通控制来实现逻辑电平的转换,其工作速度高,满足设计的要求。D触发器由时钟反连的2个D锁存器构成,同时为了减少门延迟以提高工作速度以及降低功耗,将与非逻辑门集成于D触发器内,带有与非逻辑的D触发器电路如图3所示。

1.3 可编程计数器和吞脉冲计数器设计

可编程计数器P和吞脉冲计数器S工作在分频器频率较低的频段,采用简单的异步计数器结构实现分频功能。这部分的电路一般有两种实现方式:模拟电路和数字电路,在该设计采用基于SCL的模拟电路来实现,相对于数字电路实现虽然消耗了一定的静态功耗,但电路噪声很低,版图面积小,性能更加好。整个可编程分频器结构如图4所示。

其中P计数器部分由7个带置数功能的D触发器构成;S计数器部分由2个相同的D触发器构成,另外包括2个与非门构成反馈逻辑控制预分频器的分频比;检测和置数逻辑电路由5个与门和1个或门构成。D触发器和逻辑门电路都是由基于SCL结构的模拟电路实现,全差分结构。在P计数器和S计数器中,每个D触发器构成一个2分频器,每个2分频器再级联。检测和置数逻辑的功能是使得P计数器和S计数器计数完后自动置数,这部分的设计很关键,直接影响了整个分频器的工作频率,在本文中提出了一种新的检测和置数逻辑,提高了分频器的工作性能和工作频率。以下通过对比传统的检测置数逻辑和改进后的检测与置数逻辑来说明改进后的优势。

1.3.1 传统的检测与置数逻辑设计

在传统的基于双模分频器的可编程分频器设计中,是对P计数器减计数到0时检测,并通过一定的时序逻辑产生一个置数使能信号使得P计数器和S计数器进行置数。其检测与置数逻辑电路如图5所示,当P计数器减计数到0时,P计数器中每个D触发器Qn端输出都为1,这时级联的与门逻辑输出从0跳变到1,形成一个上升沿(为一个检测信号)。这个上升沿作为带有复位功能的D触发器(DFF-RE)时钟输入,DFF-RE的复位端由4/5预分频器输出控制,即在严格的时序控制下,当检测到P计数器减计数到0时产生一个上升沿信号,此时DFF-RE打开,这个上升沿信号使得DFF-RE输出从0变为1,一段时间后DFF-RE关闭,故形成了一个置数脉冲,使得计数器重新置数。

- 基于ispPAC的滤波器设计(08-11)

- 智能手机整合近场通讯 (01-08)

- 可编程密码处理器体系结构设计(08-14)

- 软件无线电中的模数转换器(05-13)

- 直接变频接收机设计可实现多标准/多频带运行(10-11)

- 基于蓝牙芯片的无线通信模块设计与开发(02-03)