基于ARM的RFID智能安全管理系统设计与实现

时间:05-08

来源:互联网

点击:

引言

高级会议的成功举办除了对参会人员的签到、住宿、座位安排等管理外,其身份安全管理也是很重要的一方面,本文介绍了一种基于32位ARM7TDMI设计实现的射频识别[1](radiofrequencyidentification,RFID)会议智能安全管理系统,系统充分利用了ARM具有全面的、丰富的片上资源功能,用一个ARM核心板同时实现读卡、显示、声音报警、摄像和指纹等几种功能,集成了射频识别技术与生物识别技术,完成三重身份的认证,具体可选择射频+指纹模式、射频+摄像模式或射频+指纹+摄像模式。这不但大大提高了会场智能管理的安全性,而且还因ARM的集成度高而大大减少了系统电路中的器件配置,使得电路设计变得较为简单,从而使整个系统的成本大为降低,同时,系统也更安全可靠、操作更简捷。

1RFID技术概述及智能安全管理系统整体结构

RFID是一种利用射频通信实现的非接触式自动识别技术,可识别高速运动物体并可同时识别多个标签,识别的距离为几十厘米至几十米,可工作于恶劣环境,识别工作无须人工干预[2],且根据读写的方式,可以输入数千字节的信息,操作快捷方便,同时,还具有极高的保密性。RFID系统由读卡器、RFID卡和上层应用软件3部分组成,其中读卡器用来实现对RFID卡的数据读写和存储功能,由控制单元、高频通信模块和天线组成;RFID卡是一种无源的应答器,主要由一块集成电路(IC)芯片及其外接天线组成。其基本工作原理是在RFID卡进入到读卡器的射频场范围后,读卡器通过射频信号与RFID卡进行信息交互,将卡内标签中所存储的有关数据读取后提交给RFID上层软件。目前在国内外,RFID已被广泛应用于生产、物流、交通、运输、医疗、防伪、跟踪、设备和资产管理、工商业自动化、交通运输控制管理等众多领域,并不断向新的领域渗透,具有非常广阔的应用前景。

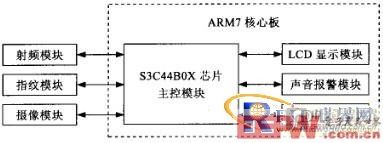

本RFID智能安全管理系统为高级会议会场设计,主要由32位ARM开发板、射频识别芯片、RFID卡、天线以及PC机应用系统组成[3],其整体结构示意图如图1所示,其中的读卡器设计是整个系统中的核心部分。

通过运行后台PC机上的应用程序,可以实现对进场人员的身份识别与验证,进场人数、进出入时间等的统计并形成报表,对缺席人员还可以通过短信的形式发与本人或将公共信息群发与有关的人。

2系统硬件设计

本系统硬件设计主要是读卡器的设计,根据需求本读卡器应是一个具有扩展功能丰富、可以独立工作,也可以联网交换信息,或者通过USB传输信息,且具有友好人机界面的嵌入式智能终端,具体设计示意图如图2所示,功能上主要包括:主控模块、射频模块、指纹模块、摄像模块、显示模块、声音报警模块和通信模块,这几大部分协同工作,完成会场信息的采集、传输与显示等操作。

读卡器中的主控模块采用ARM7核心板加外围电路板的模式,ARM7核心板采用三星公司的S3C44B0X芯片,该芯片提供的硬件资源有:2.5V的ARM7TDMI内核带有8Kcache;可选的内部SRAM;LCD控制器;2通道UART;1通道SIO;2通道通用DMA;2个提供外部请求引脚的总线DMA;8个外部中断源;有时钟功能的RTC等。具有系统管理、Cache和内部存储器、中断控制器、定时器、UART等多种功能。在该芯片上内扩了显示模块、声音报警模块和通信模块,外扩射频模块、指纹模块和摄像模块,如图2所示,另外,本ARM7核心板还扩展了8MSDRAM、2MNORFLASH、16MNANDFLASH。

射频模块由射频芯片、电源滤波部分、模拟信号滤波部分以及相应的外围电路组成,这里的射频芯片采用NXP公司(原Philips公司)的MFRC531芯片,该芯片整合了所有的13.56MHz主动非接触通信方式和协议,与MFRC500、MFRC530和SLRC400引脚兼容,支持ISO14443TypeA和TypeB的所有层的通信方案,支持使用MIFARE更高的通信波特率。内部收发器部分能够驱动近藕合设计的天线,而不需要另外活动的电路;接收部分具有高效的解调与解码电路执行机构;数字部分能处理完整的ISO14443帧数据还有错误检测功能,并且支持快速的MIFARE安全算法;具有合适的并行接口,可以直接与8位的微处理器相连,并且支持SPI兼容接口。总之,目前由于MFRC531能够满足设计需求,应用范围比其他的芯片更广,资料齐备,因此这里选择MFRC531射频接口芯片。

2.2硬件接口电路设计

2.2.1ARM与射频芯片的接口电路设计

为了能正确读取RFID卡上的数据,首先要对S3C44B0X和MFRC531的接口电路进行设计,由于S3C44B0X微处理器有足够的地址和数据总线,因此这里的接口采用独立的地址/数据总线,采用并口方式,将MFRC531的ALE引脚接高电平,将A0、A1、A2分别对应接S3C44B0X的A0、A1、A2,片选NCS信号接S3C44B0X的nGCS3,复位输入RSTPD接GPF0,通过对S3C44B0X的GPF0引脚控制操作决定射频部分的工作状态[5],如图3所示。该接口主要负责射频识别卡和管理主机PC之间的信息交换和传输,主要完成射频卡的进出控制,射频卡与应用终端之间信息联络与管理层主机通讯等功能。

另外,MFRC531与天线的接口由TX1、TX2、RX及VMID连接,TX1、TX2负责调制后的射频信号输出到天线,激励天线产生电磁波将信号输出到电子标签,而RX引脚则接收电子标签调制后由天线接收到的副载波信号,信号经过内部状态机的解调解码后成为接收到的数据。为了实现远距离的读写,最好采用环形或矩形天线,这里采用环形天线。

2.2.2ARM与其他芯片接口电路设计

在ARM核心板上通过内扩展LCD接口完成人机界面显示功能,S3C44B0X内置了LCD控制器,具有将显示缓存中的图像数据传输到外部LCD驱动电路的功能。本系统设计采用了一片74LVC164245A作为总线驱动芯片,将164245的方向控制接为高电平,S3C44B0X的信号通过164245后,再接到LCD接口上。

S3C44B0X具有IIS总线,IIS总线是一种面向多媒体计算机的音频总线,该总线专门负责音频设备之间的数据传输,广泛应用于各种多媒体系统中。本系统设计中用IIS总线输出数字音频信号到音频接口芯片,完成声音报警信息提示,这比一般采用的蜂鸣器更友好。

高级会议的成功举办除了对参会人员的签到、住宿、座位安排等管理外,其身份安全管理也是很重要的一方面,本文介绍了一种基于32位ARM7TDMI设计实现的射频识别[1](radiofrequencyidentification,RFID)会议智能安全管理系统,系统充分利用了ARM具有全面的、丰富的片上资源功能,用一个ARM核心板同时实现读卡、显示、声音报警、摄像和指纹等几种功能,集成了射频识别技术与生物识别技术,完成三重身份的认证,具体可选择射频+指纹模式、射频+摄像模式或射频+指纹+摄像模式。这不但大大提高了会场智能管理的安全性,而且还因ARM的集成度高而大大减少了系统电路中的器件配置,使得电路设计变得较为简单,从而使整个系统的成本大为降低,同时,系统也更安全可靠、操作更简捷。

1RFID技术概述及智能安全管理系统整体结构

RFID是一种利用射频通信实现的非接触式自动识别技术,可识别高速运动物体并可同时识别多个标签,识别的距离为几十厘米至几十米,可工作于恶劣环境,识别工作无须人工干预[2],且根据读写的方式,可以输入数千字节的信息,操作快捷方便,同时,还具有极高的保密性。RFID系统由读卡器、RFID卡和上层应用软件3部分组成,其中读卡器用来实现对RFID卡的数据读写和存储功能,由控制单元、高频通信模块和天线组成;RFID卡是一种无源的应答器,主要由一块集成电路(IC)芯片及其外接天线组成。其基本工作原理是在RFID卡进入到读卡器的射频场范围后,读卡器通过射频信号与RFID卡进行信息交互,将卡内标签中所存储的有关数据读取后提交给RFID上层软件。目前在国内外,RFID已被广泛应用于生产、物流、交通、运输、医疗、防伪、跟踪、设备和资产管理、工商业自动化、交通运输控制管理等众多领域,并不断向新的领域渗透,具有非常广阔的应用前景。

本RFID智能安全管理系统为高级会议会场设计,主要由32位ARM开发板、射频识别芯片、RFID卡、天线以及PC机应用系统组成[3],其整体结构示意图如图1所示,其中的读卡器设计是整个系统中的核心部分。

图1系统整体结构

通过运行后台PC机上的应用程序,可以实现对进场人员的身份识别与验证,进场人数、进出入时间等的统计并形成报表,对缺席人员还可以通过短信的形式发与本人或将公共信息群发与有关的人。

2系统硬件设计

本系统硬件设计主要是读卡器的设计,根据需求本读卡器应是一个具有扩展功能丰富、可以独立工作,也可以联网交换信息,或者通过USB传输信息,且具有友好人机界面的嵌入式智能终端,具体设计示意图如图2所示,功能上主要包括:主控模块、射频模块、指纹模块、摄像模块、显示模块、声音报警模块和通信模块,这几大部分协同工作,完成会场信息的采集、传输与显示等操作。

图2读卡器结构

读卡器中的主控模块采用ARM7核心板加外围电路板的模式,ARM7核心板采用三星公司的S3C44B0X芯片,该芯片提供的硬件资源有:2.5V的ARM7TDMI内核带有8Kcache;可选的内部SRAM;LCD控制器;2通道UART;1通道SIO;2通道通用DMA;2个提供外部请求引脚的总线DMA;8个外部中断源;有时钟功能的RTC等。具有系统管理、Cache和内部存储器、中断控制器、定时器、UART等多种功能。在该芯片上内扩了显示模块、声音报警模块和通信模块,外扩射频模块、指纹模块和摄像模块,如图2所示,另外,本ARM7核心板还扩展了8MSDRAM、2MNORFLASH、16MNANDFLASH。

射频模块由射频芯片、电源滤波部分、模拟信号滤波部分以及相应的外围电路组成,这里的射频芯片采用NXP公司(原Philips公司)的MFRC531芯片,该芯片整合了所有的13.56MHz主动非接触通信方式和协议,与MFRC500、MFRC530和SLRC400引脚兼容,支持ISO14443TypeA和TypeB的所有层的通信方案,支持使用MIFARE更高的通信波特率。内部收发器部分能够驱动近藕合设计的天线,而不需要另外活动的电路;接收部分具有高效的解调与解码电路执行机构;数字部分能处理完整的ISO14443帧数据还有错误检测功能,并且支持快速的MIFARE安全算法;具有合适的并行接口,可以直接与8位的微处理器相连,并且支持SPI兼容接口。总之,目前由于MFRC531能够满足设计需求,应用范围比其他的芯片更广,资料齐备,因此这里选择MFRC531射频接口芯片。

2.2硬件接口电路设计

2.2.1ARM与射频芯片的接口电路设计

为了能正确读取RFID卡上的数据,首先要对S3C44B0X和MFRC531的接口电路进行设计,由于S3C44B0X微处理器有足够的地址和数据总线,因此这里的接口采用独立的地址/数据总线,采用并口方式,将MFRC531的ALE引脚接高电平,将A0、A1、A2分别对应接S3C44B0X的A0、A1、A2,片选NCS信号接S3C44B0X的nGCS3,复位输入RSTPD接GPF0,通过对S3C44B0X的GPF0引脚控制操作决定射频部分的工作状态[5],如图3所示。该接口主要负责射频识别卡和管理主机PC之间的信息交换和传输,主要完成射频卡的进出控制,射频卡与应用终端之间信息联络与管理层主机通讯等功能。

另外,MFRC531与天线的接口由TX1、TX2、RX及VMID连接,TX1、TX2负责调制后的射频信号输出到天线,激励天线产生电磁波将信号输出到电子标签,而RX引脚则接收电子标签调制后由天线接收到的副载波信号,信号经过内部状态机的解调解码后成为接收到的数据。为了实现远距离的读写,最好采用环形或矩形天线,这里采用环形天线。

2.2.2ARM与其他芯片接口电路设计

在ARM核心板上通过内扩展LCD接口完成人机界面显示功能,S3C44B0X内置了LCD控制器,具有将显示缓存中的图像数据传输到外部LCD驱动电路的功能。本系统设计采用了一片74LVC164245A作为总线驱动芯片,将164245的方向控制接为高电平,S3C44B0X的信号通过164245后,再接到LCD接口上。

S3C44B0X具有IIS总线,IIS总线是一种面向多媒体计算机的音频总线,该总线专门负责音频设备之间的数据传输,广泛应用于各种多媒体系统中。本系统设计中用IIS总线输出数字音频信号到音频接口芯片,完成声音报警信息提示,这比一般采用的蜂鸣器更友好。

- 基于Zigbee技术家用无线网络的构架(12-14)

- 无线通信领域中的模拟技术发展趋势(蜂窝基站)(09-22)

- 新一代移动通信系统及无线传输关键技术(06-19)

- 蜂窝移动通信基站电磁辐射对人体影响的探讨(04-10)

- 基站升级换代中平衡性能与成本(10-06)

- 在3G与Wi-Fi之间切换 H3C 运营商WLAN解决方案(01-15)