OFDM水声通信定时同步的FPGA实现

根据相关运算的公式:

当接收到的LFM信号与本地存储的LFM信号相同时(上式中j=0),其相关值最大,出现尖锐的相关峰。图5是采用FPGA实现LFM信号相关算法的原理框图。

在发送端,一个周期LFM信号的点数为256,在接收端经过A/D采样后得到8 b的数字量,存入长度为256 B的接收缓冲区,该缓冲区设计为先进先出(First-in First-out,FIFO),作为滑动窗与本地相关序列进行相关运算。本地相关序列(存放在ROM中)与发送端发出的LFM序列相同,ROM的容量也是256×8 b。

每完成一次A/D采样,得到的8 b数据存入FIFO,然后执行一次相关运算,得到256个16 b的数据,然后将这256个数据相加,即得到此时刻对应的相关值(用24 b存储)。对得到的连续256个相关值构成的序列处理后求最大值,即可判决出接收到LFM信号的位置。3实验结果

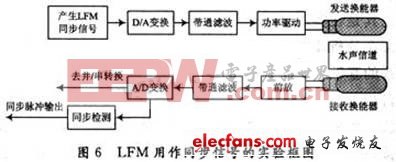

为验证LFM信号在水声通信中用作同步信号的性能,在实验室水池进行了相关实验。实验中使用的FPGA为CycloneⅡEP2C20Q240C8,考虑到半双工通信的情况,LFM信号的产生与检测在同一片FPGA中实现,共使用了3 693个逻辑单元(Logic Elements,LE),占EP2C20芯片总LE的20%。实验系统的基本框图如图6所示。

图7的示波器型号为TDS2024,各通道观测的信号如下:

CH1为发送端发出的LFM信号。由于D/A输出的信号经过带通滤波器滤波,因此信号的高频和低频部分有衰减。

CH2为接收信号(换能器输出的信号经过5 000倍放大和带通滤波处理后)。

CH3为接收端FPGA检测到LFM信号后的同步脉冲输出。

由图7可以看出:该方案实现了LFM信号的产生,在多径较为严重的实验室水池中,在接收端正确完成了对LFM信号的同步检测,可以较准确地提取到LFM信号的相关峰位置,证明该方法作为OFDM水声通信系统的定时同步方案是可行的。

FPGA 实现 同步 定时 水声 通信 OFDM 相关文章:

- 基于FPGA的短波通信接收机(11-19)

- FPGA的低功耗设计(07-06)

- EDA环境衔接测量软件(06-25)

- Altera 28nm FPGA助力NEC提升LTE基站性能(11-19)

- 基于FPGA的BPSK信号载频估计单元设计(09-02)

- FPGA推动5G异构无线网络(09-28)