通用网络协议一致性测试平台的设计与研究

摘要:针对我国当前网络互连、互通的迫切需求,提出了一种通用的网络协议一致性测试平台的设计方案。通过对通用平台硬件结构和软件设计的说明,阐述了通用平台的工作过程和测试方法,为网络协议一致性测试提出了有效的解决方案。

关键词:通用平台;协议;一致性测试

0 前言

计算机网络协议一致性测试是检验计算机网络各部分正确互连、互通和互操作的关键技术,用来验证产品协议实现与相应协议标准之间的一致性。即在同一网络协议标准下检验不同的待测设备是否在相同的外部输入下,输出相同的结果。

目前, 我国网络产品检测的技术水平和能力与国际上存在较大差距,协议一致性测试产品的设计大多停留在测试方法的理论研究上,在协议测试的通用平台方面还缺乏较好的解决方案。

1 网络协议一致性测试概述

网络协议的一致性测试是一种功能性的黑盒测试,通常包括静态测试和动态测试两类。静态测试是指协议实现者向测试方提交“协议实现一致性声明”与协议中的静态一致性要求相比较,动态测试是运行测试集对DUT(Device under Test)进行测试。

协议一致陛测试包括三个阶段:第一阶段是测试生成,为特定协议产生独立于所有协议实现的抽象测试集;第二阶段是测试实现,把抽象测试集中的测试例转换成可执行的测试例;第三阶段为测试执行,在特定的DUT上执行测试用例。

通用网络协议一致性测试平台用于动态测试,也分为三个阶段:第一阶段是对一个指定的协议生成一个测试套集,根据协议的要求,这个测试套集可以在实现前对收发双方进行的交互进行完全设定,或者在某些需要双方互动(字段值需要对方的数据来进行填写)的字段给出一个变量。第二阶段是按照这个测试套集对被测设备的协议实现(DUT)进行黑盒测试;第三个阶段是通过比较DUT的实际输出与预期输出的异同,从而实现网络协议的一致性测试。

通用平台对各个不同的协议可支持生成不同的测试套集,分别进行测试和一致性对比。

2 通用平台组成

通用平台由控制台、测试机两部分组成。其中控制台负责配置测试套集的策略、测试结果的统计分析及人机交互;测试机负责生成或接收测试套集,然后生成测试流发送到被测设备;并从被测设备接收测试数据;然后将数据返回控制台。如图1所示。

2.1 控制台

控制台硬件可以是一台PC机,其网卡与测试机控制口相连。在高层通过人机对话界面,对协议、算法及网络参数进行配置,对测试套集生成模式及使用方式等进行策略设置;通过驱动程序与测试机进行通信,向测试机输入测试套集的参数配置,并接收测试机输出的结果;并对测试结果进行统计分析。

软件模块包括界面模块、协议接口模块、算法接口模块、网络接口模块、通信模块、统计分析模块。

2.2 测试机

2.2.1 硬件组成

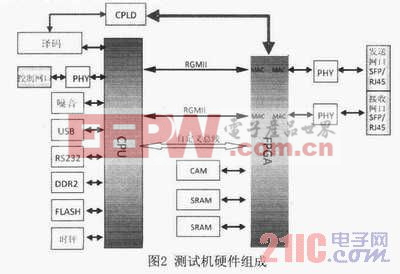

测试机硬件采用高性能、高可靠性、高稳定性的嵌入式多核处理器平台。配置高速100M、1000M自适应以太网口,可扩展的大容量DDR2内存和大容量的Flash空间。硬件框图如图2所示,多核处理器平台的核心部件为CPU、CPLD和FPGA。

CPU主要用于接收来自控制机的网络、协议、算法参数并生成实现网络协议的测试套集,它可以直接对被测设备发送或者接收测试流,或者通过自定义总线将测试套集存储在SRAM中,以实现快速的测试;它还实现对外围配套器件的控制,包括DDR、Flash、噪声、日历时钟以及译码等。CPU的PCI总线转换出一个网络,作为测试机的控制口,与控制机进行通信。CPU的串口总线接出一个RS232串口。

CPLD主要用于CPU启动、数据总线的译码、FPGA逻辑配置等处理。

FPGA主要用于网络接口处理和测试流发送、接收。首先,它提供两个软MAC核与PHY芯片相连实现DUT的发送和接收网口;其次,它提供另外两个软MAC核可以允许CPU直接与DUT进行发送接收测试流;也可以调用外部SRAM实现测试流发送接收等操作。FPGA和CPU之间有两种不同的通讯接口,一种是数据总线接口,用于传输基本配置信息、状态信息和SRAM数据;一种是RGMII网口接口,用于传输测试流数据。

2.2.2 软件组成

CPU软件使用裁剪的定制LINUX操作系统,内核版本2.6以上,配IPv4协议栈等。CPU要实现的软件功能比较多,软件模块有以下几个:

(1)与控制机的通信模块:负责接收来自控制机的网络、协议、算法参数以及其他命令,并回送测试结果。

(2)算法实现模块:实现协议中需要的算法。

(3)套集生成模块:这是实现一个协议所需要的IP包的集合,包括发送的IP包和接收的IP包。每个不同的协议将产生定制的套集。每个套集的主要流程就是生成指定的某个协议所需IP包的过程。但是在协议的实现上,会按照协议的要求对相应的字段进行边界测试、正确性和错误测试。并体现在不同的测试流里。

(4)测试流发送模块:将存储在SRAM里的测试流发送至DUT。

(5)测试流接收模块:接收DUT发出的响应流,存储在SRAM里。

(6)结果的协议分析模块:CPU接收到测试流后,将其按照协议要求拆分成各个字段,并与协议进行比对分析。并将结果发送到与控制机的通信模块。

在发送IP包和接收IP包有关联的情况下,比如IV向量由接收包传递过来后才能确定下一包发送的内容,必须由CPU直接进行测试。

在协议比较简单,发送IP包和接收IP包没有关联的情况下,可以将测试套集装载在SRAM里,由FPGA进行测试。这种情况下,也可以测试DUT的性能。

3 工作流程与测试内容

协议一致性测试的主要过程包括:标准测试套集生成、测试执行、结果分析三个部分。标准测试套集是通过分析协议来确定要测试的各个方面,从而产生测试用例的集合;测试执行为测试用例的运行过程;接收数据分析是对测试结果进行分析,从而得到协议实现与协议说明是否一致的判决。如图3所示。

平台 设计 研究 测试 一致性 网络 协议 通用 相关文章:

- 智能手机差异化从主平台到外围(05-10)

- Telefonica新智能测试平台整合M2M通信测量(02-21)

- 以软件为核心的无线测试平台的设计(03-18)

- 支持终端一致性测试的TD-SCDMA协议测试平台(03-28)

- 基于ARM平台的RFID中间件系统设计(05-16)

- 物联网跨平台设计如何做?十大策略来帮你!(02-03)