TMS320F28335与串行A/D转换器ADS7863的接口设计

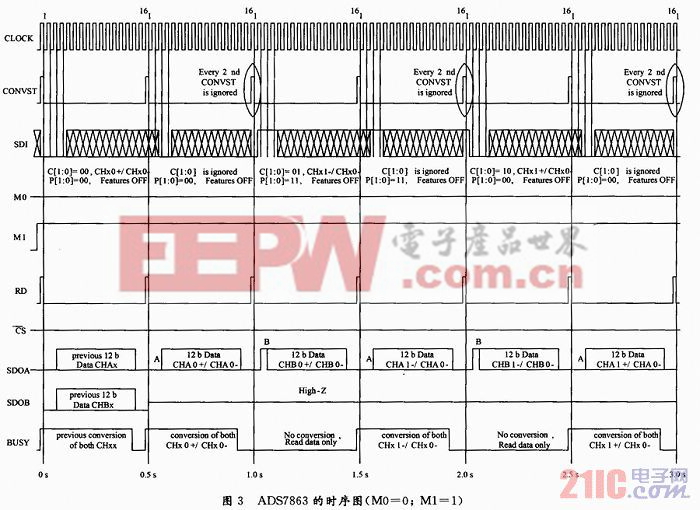

相应的时序图如图3所示。

3 TMS320F28335 McBSP与ADS7863接口设计

3.1 硬件接口设计

图4是TMS320F28335 McBSP与ADS7863无缝连接的示意图。从图中可以看出,McBSP与ADS7863之间的连接非常简单,实现了数据的高效转移,充分体现了同步串口连接的优点。由F28335 DSP的GPIO11向ADS7863提供片选信号。McBSP的数据发送DX脚接ADS7863的SDI脚,向ADS7863发出控制信号。ADS7863的SDOA脚接McBSP的数据接收DR脚,向F28335传送数据信号。由MeBSP内含的可编程采样率发生器生成时钟信号CLKG和帧同步信号FSG。由CLKG驱动发送时钟信号CLKX,CLKX驱动接收时钟信号CLKR和ADS7863的时钟信号CLOCK。由FSG驱动发送帧同步信号FSX,FSX驱动接收帧同步信号FSR和ADS7863的开始转换信号CONVST。CONVST初始化一个转换进程,并启动发送前一周期转换的数据。为了简化,只连接了ADS7863的CHA1+和CHB1+通道,可用输出数据的第二位(ADC指示符)分辨所采样的信号来自哪个通道。

3.2 软件接口设计

3.2.1 McBSP口初始化

整个初始化过程包括三部分:接收部分初始化、发送部分初始化和采样率发生器初始化。

(1)DSP初始化后,采样率发生器的初始化位GRST=0;在其他情况下,也可通过向SPCR2寄存器中的GRST位置0,使采样率发生器处于初始化状态。在此状态下,时钟CLKG时钟为CPU时钟的1/2,帧同步信号FSG为逻辑0;设置接收初始化位RRST、发送初始化位XRST和帧同步发生器初始化位FRST为0;

(2)对采样率发生器SRGR[1,2]进行设置,并对其他控制寄存器进行设置;

(3)等待两个CPU时钟以确保内部正确同步;

(4)将采样率发生器初始化位置1,使采样率发生器进行工作;

(5)等待两个SRG时钟;

(6)将接收和发送初始化位置1;

(7)在下一个CPU时钟的上升沿,CLKG时钟发送一个1,并以CPU时钟/(1+CLKGDV)的频率运行;

(8)在数据发送寄存器DXR[1,2]被载入数据后,将帧同步初始化位置1以发出正确的帧同步脉冲信号。

下面是McBSP初始化程序片段:

3.2.2 McBSP串口通信主要程序

McBSP串口通信主要程序如下:

4 试验结果

ADS7863的输入模拟量Vin1=1.670 V,Vin2=1.866 V时,A/D转换器SDOA引脚输出如图5所示。图中通道Ch2为ADS7863的外部输入时钟CLOCK,通道Ch1为ADS7863的模拟输入通道CHA1+和CHB1+的32位输出结果。可以很清楚地看出该32位二进制码为:00110101011010000111011 111101000,前16位为CHA1+通道的转换结果,后16位为CHB1+通道的转换结果。在本试验中,通过设置McBSP的采样率发生器时钟分频系数CLKGDV,使得McBSP的采样率发生器时钟CLKG频率为323.2 kHz,从而使得ADS7863的外部输入时钟CLOCK频率为323.2kHz。

本文设计了高速度、高精度12位A/D转换器ADS7863与32位浮点DSP TMS320F28335的McBSP之间的硬件接口与软件实现。该系统设计简洁,在DSP集成开发环境CCS下采用C语言编写、调试完成,对其他A/D系统设计具有很大的借鉴意义。

接口 设计 ADS7863 转换器 串行 TMS320F28335 相关文章:

- 巧用测试仪器解决错综复杂的无线网络问题(05-16)

- 怎样选择适合您应用的无线网络(10-10)

- 电路保护器件保护移动设备避免ESD影响(04-22)

- 基于FPGA水磁无刷直流电机控制电路(04-28)

- 如何顺利通过电磁兼容试验(04-16)

- 高速电路设计中时序计算方法与应用实例(04-28)