一种虚拟仪器通用以太网接口设计

虚拟仪器以其性价比高、开放性强等优势迅速占领了市场,并成为测控仪器新的经济增长点。步入信息化时代最显著的标志就是信息网络在各行业中的渗透和普及,其中以太网最为典型。以太网总线有可能代替现行的其他总线方式而成为虚拟仪器数据采集系统的首选接口。

1 以太网接口的总体设计

1.1 以太网接口设计方案选择

以太网接口的设计通常有三种方案:其一是采用FPGA实现物理层、网络层、接入层和传输层等各层的描述,该方案要自行实现复杂的TCP /IP协议,难度较大;二是基于物理层网络控制器和微处理器来实现网络传输,该方案的优点是灵活性强,可以针对不同的系统采用不同的协议,可实现协议的精简:三是采用专用的协议处理芯片实现以太网数据传输,该方案的硬件电路相对简单,开发周期短,并有越来越多的芯片可供选择,且集成了多种协议,使用十分方便。

本设计采用第三种接口方案,即采用专用的TCP/IP协议集成芯片,并由FPGA实现对协议处理芯片的控制,从而实现以太网数据传输。协议处理芯片选用内部固化了TCP/IP协议的W3150A+并配合物理层芯片RTL8201,该方法硬件电路相对简单,并可利用逻辑硬件实现,从而使系统设计更加简单、紧凑。

1.2 以太网控制芯片W3150A+简介

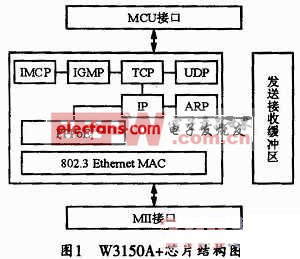

W3150A+是WIZnet公司专门为以太网互联和嵌入式系统推出的TCP/IP协议栈芯片。W3150A+能够实现TCP、UDP、IP Ver.4、DHCP、ARP和ICMP等协议,同时,网络接口层(包括MAC子层和DLC子层)也可在该芯片中实现。同时还能提供四路网络连接,其内部有16KB的双口RAM可作为数据缓冲区,并可支持全双工模式,同时带有标准的MD接口,可方便连接物理层接口芯片。此外,WIZnet公司还提供了Socket API程序包,可以加速应用程序的开发。

图1所示是W3150A+芯片的结构框图。由图1可见,W3150A+主要由4部分组成。其中第一部分是MCU接口。W3150A+提供有直接总线接口、间接总线接口和SPI总线接口。既适合与类似8051单片机的总线连接,也非常适合与只有IO口而没有总线接口的控制器连接;第二部分是TCP /IP协议栈。W3150A+已经完全固化了从MAC层、网络层到传输层所需要的协议,因此,用户无需了解这些协议的具体实现方法和实现代码;第三部分是接收和发送缓冲区,通过以太网进行通信的数据就是通过这些缓冲区来交换的;第四部分是以太网物理层接口(MII接口)。W3150A +可以与物理层芯片RTL8201无缝连接,从而实现10/100BaseT以太网物理接口。

W3150A+内部的寄存器分为两个存储器和两类寄存器。两个存储器分别用于数据传输的输入和输出,两类寄存器分别是通用寄存器和端口寄存器,每类寄存器都含有大量的状态字控制寄存器。下面简要介绍比较重要的状态字控制寄存器。

Sn_MR:端口n模式寄存器,该寄存器用于设置端口的选项或协议类型;

Sn_CR:端口n命令寄存器,该寄存器用来设置端口的初始化、关闭、建立连接、断开连接、数据传输以及命令接受等;

Sn_IR:端口n中断寄存器,该寄存器用于显示建立和中止连接、接收数据、发送完成以及时间溢出等信息;

Sn_PORT:端口n的端口号寄存器,该寄存器可在TCP或UDP模式下设定对应的端口号;

S_TX_FSR:端口n发送存储器剩余空间寄存器,该寄存器用于指示用户可以使用的发送数据空间的大小,在发送数据前,用户必须先检查剩余空间的大小,然后控制发送数据的字节数;

Sn_TX_RR:端口n发送存储器读指针寄存器,该寄存器用于指示端口在发送过程完成后发送存储器的当前位置。当端口n的命令寄存器收

到SEND命令后,可随即从当前Sn_TX_RR到Sn_TX_WR的数据中发送出去,发送完成后,Sn_TX_RR的值自动改变;

Sn_TX_WR:端口n传输写指针寄存器,该寄存器可指示向TX存储器写入数据时的地址;

Sn_RX_RSR:端口n接收数据字节数寄存器,该寄存器只是端口接收数据缓冲区接收数据的字节数,通常可由Sn_TX_RR到Sn_TX_WR的值计

算得出,向端口n命令寄存器写入RECV命令后,寄存器的值将自动改变,并可以接收远程对端的数据;

Sn_RX_RD:端口n接收缓冲区读指针寄存器,该寄存器只是端口接收过程完成后的读地址信息。

W3150A+内部有4个独立的端口(Socket),它们的状态、控制分别映射在第二到第五寄存器区。主要用于实现端口工作模式的控制(TCP服

务器、TCP客户端、UDP或PPPOE等)、设置该端口的端口号,设置该端口目的主机IP地址和端口号,以及端口接收和发送数据控制等。

2 以太网接口的硬件设计

本接口的硬件设计主要包括FPGA与W3150A+的接口设计,物理层芯片RTL8201与W3150A+的接口设计以及时钟模块和电源模块的设计。其硬件设计框图如图2所示。

- 巧用测试仪器解决错综复杂的无线网络问题(05-16)

- 怎样选择适合您应用的无线网络(10-10)

- 电路保护器件保护移动设备避免ESD影响(04-22)

- 基于FPGA水磁无刷直流电机控制电路(04-28)

- 如何顺利通过电磁兼容试验(04-16)

- 高速电路设计中时序计算方法与应用实例(04-28)