基于分布式运算(DA)结构的查表法

过程中大量减少乘法运算,而乘法运算在硬件程序中往往是占用资源最大的部分之一。运用DA处理结构能大大减少硬件资源,并在很大程度上提高程序运算速度。

为了进一步减小LUT的个数,现在在过采样中引入零抽样值。设u(n)为过采样程序块的输出序列:

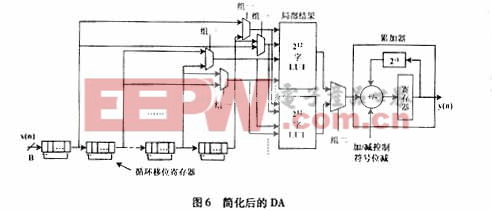

类推,应用u(n)后,48个抽头中的36个采样值将给定为零,这样就有一半的加法器输入为零采样值,并在每个时钟将零采样值传递到对应的乘法器。而另一半加法器的输入值中也只有一个是非零采样值。这样一来,在第一级就能减少24个加法器和一半的乘法器,也就意味着运算出一个输出采样值只需调用一半的滤波器系数。对一个码片速率输入采样值x(n)来说,经过运算得出4个输出采样:y(n)、y(n+1)、y(n+2)以及y(n+3),其中y(n)和y(n+3)需要调用的系数(组一)如下:h(0)、h(3)、h(4)、h(7)、h(8)、h(11)、h(12)、h(15)、h(16)、h(19)、h(20)、h(23);而y(n+1)和y(n+2)需要调用的系数(组二):h(1)、h(2)、h(5)、h(6)、h(9)、h(10)、h(13)、h(14)、h(17)、h(21)、h(22)。这样就可以完成如图6所示的实效DA。输入序列即为码片速率采样值,并且输出的数据是码片速率的4倍,每输入一个采样值可以得出4个输出采样值,内部时钟速率为4×B×码片速率。DA运行中,常用电路移位寄存器(CSR)来代替一个移位寄存器保存数据,直到每个芯片间隔运算出最后的输出采样值为止。一旦输入一个新的采样值,这些CSR就要更新一次。在芯片的持续时间中一共有4个循环,每个循环经历B个时钟并产生一个输出采样值。一个循环过后,CSR移位回归到初始数据,为下一个循环处理做准备,以生成另一个输出采样值。图6中的2个LUT分别存储了两组滤波器系数各自生成的局部结果。选择器是用来决定在每个循环中选择这两组输入分支的哪一组的,其中当高位LUT的结果在循环1和2输出,低位LUT结果在循环3和4输出的时候选择组一;当高位LUT的结果在循环1和4输出,低位LUT的结果在循环2和3输出的时候选择组二。累加器的寄存器在每个循环的起始都要进行清零。

四、设计

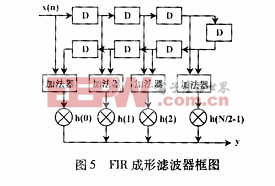

现设计一个1比特输入、14比特输出的平方根升余弦滚降线性相位FIR数字滤波器,滚降系数为0.22,带外衰减要求大于45 dB,即通带内(f8.192MHz)的起伏小于0.5dB,阻带外(f>10 MHz)的衰减大于45dB。在设计中选用了Alter公司的FPGA芯片-EP1K50QC208-3,该芯片有2 880个逻辑单元(LE),40960个片内存储器。本设计占用了387个LE和1088个片内存储器,分别占总资源的1.3%和2%。

经过试验,本结果已经在FPGA中得到了实现。

五、结 论

从试验结果中可以看出,DA实现控制起来比较简单并且时钟速率较低,但是因为LUT的大小会随着滤波器阶数的增加呈指数增长,因此其门的数量也较多。在阶数很大的滤波器中采用并行的FIR结构,每个并行的子滤波器以DA结构实现,这样,控制起来就稍微有点复杂了。因此,如何去克服这方面的缺点还有待于继续研究。

- LTE-SAE体系结构及性能剖析(1)(07-07)

- LTE-SAE体系结构及性能剖析(2)(07-07)

- 绿色通信的基站体系结构设计(04-18)

- 详细解析无线局域网(WLAN)技术(02-05)

- 软件无线电结构及其电磁兼容(03-07)

- PBG结构的微带贴片天线设计(03-26)