USB 3.0中的CRC校验原理及实现

摘要:循环冗余(CRC)是USB协议中重要的错误检测措施。在此分析了USB 3.0数据包的基奉格式以及USB 3.0协议中CRC校验的特点,针对USB 3.0数据高速传输的要求,设计实现并行发送端CRC产生和接收端CRC校验电路,功能仿真结果证明了其有效性。

关键词:USB 3.0;CRC校验;Verilog HDL代码;仿真结果

在通用串行总线(USB)的数据传输过程中,数据循环冗余校验(CRC)是为了保证数据传输中数据的正确性而采用的数据保护方法。USB 3.0协议中为了检测和减少这类错误,一方面提供了一系列硬件和软件措施,以保证数据传输的正确性;另一方面在每个包中加入检测位来发现这些瞬时的错误。协议中对每个包的控制位和数据位提供了循环冗余校验,若出现了循环冗余码的错误,则认为该包已经损坏。

本文介绍了USB 3.0设备控制器中的协议层在数据收发时,如何采用并行电路来完成数据包发送时CRC码的产生和接收时CRC码的校验,并行处理方法与常用的串行处理相比,极大地降低了功耗和电路综合的难度。

1 USB 3.0中的CRC校验

USB 3.0协议规定了4种类型的包:链路管理包(LMP),传输包(TP),数据包(DP)和同步时间戳包(ITP)。链路管理包(LMP)只遍历直接连接的端口,主要用于管理该连接。传输包遍历主机和设备路径中的所有链路,用来控制数据包流,配置设备和集线器等,传输包没有数据部分。数据包遍历主机和设备路径中的所有连接。同步时间戳包是一个多播数据包,由主机发送到所有激活的连接。

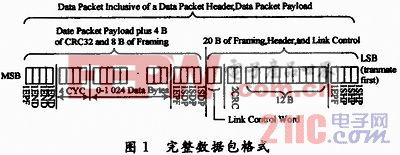

USB对所有传输数据的保护采用了CRC校验和数据重传的方式。当通过检错码判断错数据包错误时,发送端通过重发来达到纠错的目的。 USB 3.0数据包由数据包头(DPH)和数据包有效载荷(DPP)两部分组成,DPH类似于一个传输包,DPP中有一个32位CRC(CRC-32),可以确保数据的完整性。数据包以16 B的数据包头开始(有的包只有包头没有数据部分),包头含了如何处理该包的信息。一个完整的USB 3.0数据包的格式如图1所示。

在数据包头(DPH)中,有一个长度为2字节16位的CRC校验码对数据包头的12个字节信息进行保护。在数据部分(DPP)中,包含最大1 024 B的数据,有一个长度为4 B 32 b的CRC校验码对数据部分进行保护。另外,在数据包头中,有2 B的链接控制字(Link Control Word),其中长度为5位的CRC用来对链接控制字中其他的11位信息进行保护,格式如图2所示。

在USB 3.0协议中,CRC校验有以下特点:

(1)在发送端,CRC校验在初始状态时将余数寄存器的值置为全1,如果没有这样的预设置,就不能正确地保护数据包开始为0的数据位。在接收端,也同样将移位寄存器预设为全1状态,以保证接收到的被除数加上一个相同的常数,如果数据传输无误,则余数产生器应该得到相同的余数。

(2)采用了3种类型的CRC校验:5位、16位和32位CRC校验。5位CRC校验采用的生成多项式为;G(X)=X5+X2+1,如果准确无误地接收到数据,接收端的5位余数应该是01100;16位CRC校验采用的生成多项式为:G(X)=X16+X15+X2+1,接收端的16位余数应该是10000000000001101;32位CRC校验采用的生成多项式为:G(X)=X26+X23+X22+X16+X12+X11+X10+X8+X7汁X5+X4+X2+X1+1,接收端中的32位余数应该是32’HC704DD 7B。

(3)发送端对输入的数据作除法运算后,将所得到的余数按位取反,取反后的余数放在待发送数据的高位,组成了新的数据流。接收端CRC校验采用与CRC产生相同的算法来实现,只是作为输入数据的是原始的被除数数据和对应的CRC校验码组成的新数据流。如果接收端的余数与(2)的要求一致,则说明接收端准确无误地接收到了数据。

2 并行CRC校验的设计

在USB 3.0协议中,数据最高传输速率高达5 Gb/s,串行方法无法满足实时性要求。本文中,CRC校验采用的是并行设计方法。

在USB 3.0协议中,数据收发是以字节为单位来传输的,所以在发送端和接收端可以通过一个8位移位寄存器将串行数据转换成字节表示形式,然后再对数据进行并行的CRC码产生和校验。

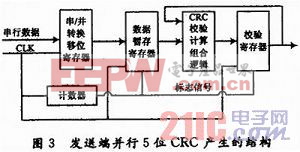

以链接控制字中的5位CRC为例,发送端并行CRC产生的设计结构如图3所示。计数器用于产生标志信号,计数值为8时串并转换结束。数据暂存寄存器获取字节数据,经组合逻辑计算后产生新的校验寄存器值。并行CRC5的余数多项式表达式如下:

在接收端,按照和发送端同样的电路,对发送端产生的CRC校验码和输入的数据一并进行CRC校验,如果接收端成功接收,最后得到的CRC校验码为常数(01100)。

3 仿真结果

发送端和接收端的并行CRC产生和校验设计用Verilog HDL实现,用ModelSim工具进行仿真,发送端并行CRC产生和接收端CRC校验的仿真波形分别如图4和图5所示。在发送端,每输入8个数进行一个并行的CRC5计算,crc_d寄存器的值随发送的数不断更新,直到最后产生一个余数,在接收端将该余数和发送端的数一并进行CRC5校验,最后CRC得到一个常数值01100。

- 基于光纤到户技术实现智能小区三网融合(05-14)

- 基于DDC和DUC的大带宽DRFM设计与实现(04-24)

- 电子引信检测设备实现通用化应用(04-17)

- 融合是实现新一代门禁及电脑桌面登录安全性的关键(02-26)

- 基于基站定位和 GPS 的双定位跟踪系统架构和实现(12-19)

- 利用RF预失真实现功放线性化(12-14)