一种高可靠性的计算机与FPGA串行通信的实现

摘要:主要介绍以FPGA为硬件平台的下位机与计算机(上位机)进行串行通信,将串口功能集成到单片FPGA内,运行中波特率可调,经过适当的倍、分频实现了零误差的波特率发生器,提高了数据传输的可靠性。上位机上编写VB程序负责主设备的发送命令并接收显示来自FPGA回发的数据,实验结果表明通信可行,可靠性高。

关键词:FPGA;串行通信;VB;可靠性

串行通信广泛应用于数字通信和工业控制领域,传统的专用串口通信芯片接口复杂,体积较大,随着微电子技术的发展,FPGA的等效门数迅速增加,可以完全将串口功能集成在单片FPGA内,减少了外围电路的体积,降低了设计的复杂性,同时也提高通信的可靠性。

1 串行通信的原理

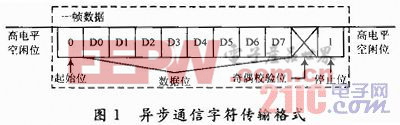

串行通信是指通信的发送和接收方之间数据信息的传输是在单根数据线上完成,以每次一个二进制的0或1为最小单位逐位进行传输,本文采用异步的全双工通信方式,数据传输是以字符为单位,如图1所示为异步通信的帧格式。

其中,一帧数据包括起始位、数据位、校验位和停止位。线路空闲状态下,发送和接收端均保持高电平;通信开始时,通信一方发送一个起始位(低电平),表示通信的开始,紧接着发送有效的数据位,通常约定的数据位有5,6,7或者8位,根据用户需要进行设定,然后发送校验位,这里选用偶校验,最后发送停止位,可以是1,1.5或2位不等,用户自行约定即可。本文选用8位数据位、偶校验、1位停止位,可以实现所有字符的收、发。

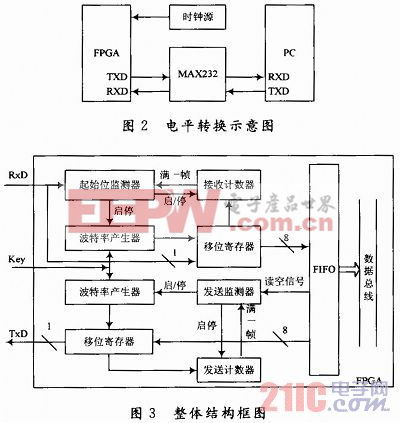

串行通信传送数据是按位顺序进行,最少只需要一根传输线即可完成,要实现全双工的通信共需要2根数据线和1根接地线即可,通信双方可以在同一时刻进行发送和接收的操作。本文采用的是RS 232C串行接口标准,是目前PC机与通信工业中应用最广泛的一种串行接口。但计算机的串口是用正负电压来表示逻辑状态,与FPGA电路板上以高低电平表示的逻辑状态的标准不同。因此,为了能够同计算机进行通信,必须在两者之间进行电平的逻辑关系转换,本文采用集成电路芯片MAX232来完成两种电平的双向转换。如图2所示。

2 FPGA收发模块的实现

要使FPGA具有数据的收发功能,则收、发两模块必不可少,与此相关联的还需要收、发的时钟即波特率产生器,收发监视器以及输入/输出缓冲器。本文采用先进先出存储器(First in First Out,FIFO)作为收发数据的双向缓冲器。如图3所示为FPGA实现串口数据收发的整体框图。收、发模块原理基本相同,只是发送区的发送控制信号受FIFO的读空信号控制。本文重点介绍接收数据的过程。

2.1 接收区模块

接收区模块负责数据的串行接收并转换为并行数据,然后送入FIFO存储器以备后用。它主要由起始位检测模块、波特率可调的波特率产生模块和接收模块组成。

(1)波特率产生器

串行通信的传输受到通信双方配备性能及通信线路的特性所左右,收、发双方必须约定相同的速率进行串行通信,即收、发双方采用相同的数据传输速率,就仪器和工业场合来说,最常见的数据传输率有4 800 b/s,9 600 b/s等,现在个人计算机提供的串行端口的数据传输率甚至达到115 200 b/s。若传输距离较近且设备提供的情况下使用最高的数据传输率。本文所列的波特率产生器灵活多变,可以根据实际条件选择不同的数据传输率。设计中添加了一位拨码开关(Key),故运行中可以在两种波特率中进行选择。这里选用了4 800 b/s,9 600 b/s两种常见的数据传输速率,当Key为低电平时选择4 800 b/s,为高电平时选择9 600 b/s。当然,以此类推运用二个拨码开关即可实现4种波特率的互调等。

本文采用50 MHz时钟源,所以要得到4 800 b/s和9 600 b/s的传输率分别需要进行5 208次和31 250次分频。分频参数如表1所示。从表中第1,3两行可以看出如果只用系统提供的50 MHz时钟源,得到的两种波特率均存在误差0.006 4%。可以灵活运用倍、分频原理进一步减小误差。从表中第2,4行可以看出,当时钟提高到150 MHz时,两种数据传输率的分频系数刚好能取到整数,也就是说实际可以得到理想的数据传输速率。但从50~150 MHz需要经过3倍频,如果硬件允许的情况下可以采用3倍频,能够使传输可靠性更高,本文采用的就是此方法。由于设计中采用的硬件是Altera公司CycloneⅡ系列FPGA,拥有2个锁相环,可以进行灵活的倍、分频,所以能够满足3倍频的要求。

(2)起始位检测器与接收模块为使得程序清晰,这两个模块用状态机进行实现,如图4所示。系统复位后进入空闲状态,空闲状态时起始位检测器不断检测接收管脚(RxD)上的信号,当检测器检测到低电平到来后,状态转移到接收状态,接收模块

- 无线通信领域中的模拟技术发展趋势(蜂窝基站)(09-22)

- 新一代移动通信系统及无线传输关键技术(06-19)

- 蜂窝移动通信基站电磁辐射对人体影响的探讨(04-10)

- 无线升级到802.11n 应考虑的因素有哪些?(10-30)

- 第四代移动通信系统中的多天线技术(08-05)

- 4G移动通信系统研究进展与关键技术(12-24)