声纳信号处理中UDP协议数据传输研究与设计

摘要:为了在声纳系统中通过以太网口进行大批量、高速率的数据传输处理,在FPGA中硬件实现了嵌入式UDP协议栈,完成了架构设计、软件仿真验证及硬件实现。用FPGA硬件实现UDP协议栈,加速了网络数据处理能力,使信号传输速率达到了80MB/s,实现了千兆级通信,很好地提高了声纳系统中数据传输速率和系统性能。同时,用FPGA硬件实现UDP协议,栈减小了PCB版图面积和布局布线复杂度,提高了开发效率,有效地降低了开发成本。

关键词:UDP协议;FPGA;数据传输;信号处理

0 引言

UDP协议是一个简单的面向数据报的传输层协议,提供不呵靠的传输层服务。它只负责将应用数据打包交给网络层,但是不保证数据报能正确到达。UDP协议提供了一种最简单的基于数据包的、不可靠的传输机制。其特点是以数据包为最小传输单位,并且没有任何流量控制机制,适合传输效率要求较高且对传输可靠性要求不高的情况。

现有XXX型号声纳系统需要实现Link口转UDP格式数据传输,以满足大批量、高速率的数据传输要求,现有的CPU和软件协议栈无法满足此要求。经仔细研究,发现用FPGA硬件实现UDP协议栈,可以很好地提高数据传输速率,满足该声纳系统的性能要求。本文实现了一种可配置、可重用的硬件UDP协议栈,完成了UDP协议的FPGA设计:设计了UDP发送端模块,UDP接收端模块以及Link端模块等,同时对所设计系统进行了验证。经过实际验证,系统数据通信速率达到了80 MB/s,实现了千兆级以太网通信,很好地提高了声纳系统中数据传输速率和系统的性能,满足了XXX型声纳系统对大批量、高速率数据传输的要求。并且,此方案减小了PCB版图面积和布局布线复杂度,可以移植到任何其他的FPGA设计中,使开发效率得到了极大的提高,有效地降低了开发成本。

1 声纳系统信号处理中UDP协议的FPGA设计

1.1 UDP模块设计

UDP包头包括IP,端口号,UDP包长度,CHECKSUM四个部分。并且UDP信息包的标题很短(标题即头部),只有8 B,其中,源端口(2 B)、目的端口(2 B)、长度(2 B)、校验码(2 B)。这里设计的架构通过发送端对数据进行打包,通过接收端进行解包。

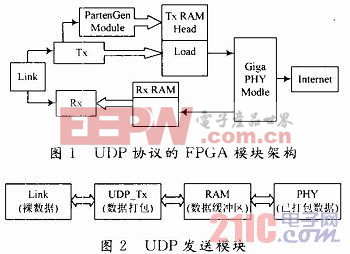

UDP协议的FPGA架构如图1所示。

发送端(Tx)是头信息生成模块,从Link口发出的数据传入发送模块Tx内。然后,发送模块Tx中的裸数据发送到数据缓冲区RAM中,经由PartenGen模块在数据前面添加首部,即为数据进行传输层协议UDP打包。传输层协议打包好的数据传输到物理层模块,通过物理层调节芯片传送到以太网口。发送完成后,发送模块恢复空闲状态,等待下一次数据发送。在发送过程中,传输数据的IP地址是固定的。UDP发送过程没

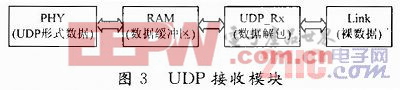

有可靠性的保证机制,只是进行数据的打包传输。发送模块结构图如图2所示。

外部数据从以太网口经过物理层传入到接收端的数据缓冲区RAM中,外部数据是UDP格式的数据。接收模块Rx从数据缓冲区RAM中提取数据,在提取的过程中,Rx模块中的应用程序将UDP格式的数据的首部去除,只提取有效载荷部分。根据UDP数据包中的目的端口号,Rx将去UDP格式化的裸数据发送给Link口,完成接收端模块的功能任务,其示意图如图3所示。

1.2 Link模块设计

在发送过程中,外部数据经过Link口传输给发送模块(Tx)进行打包处理,然后传输至MAC。Link端模块设计如图4所示。

当acki为0时开始进行数据传输。工作时,有3个时钟输入:Link口时钟clk和clk270,以及系统本地时钟clk4。其中,clk4的频率是Link口时钟的1/4。Link的时序效果图如图5所示,在时钟的卜升沿与下降沿进行数据存写。双倍速率的数据通过Link后被分为单倍速率的数据写入UDP发送端Tx中。从Link出来的数据传入发送端Tx时,时钟每跳变一次,地址增加一次,发送端Tx将增加的地址写入到数据缓冲区RAM中,进行打包。

2 系统实现

本文在FPGA中对所设计的系统进行了验证与硬件实现。发送过程的QuartusⅡ8.0仿真波形图如图6所示。

接收过程QuartusⅡ8.0仿真波形图如图7所示。

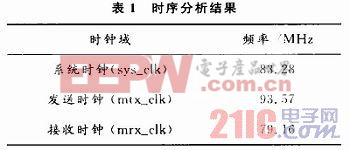

本系统中FPGA选用的是Altera公司的EP2S60F672C5。系统有3个时钟域:系统时钟、发送时钟、接收时钟。其时序分析结果如表1所示。

从表1中可以看出,系统时钟为83.28 MHz,发送和接收时钟分别达到93.57 MHz,79.16 MHz。因此,整个系统能够满足80 MB/s的速率要求。

3 结语

本文提出采用FPGA实现UDP协议栈,完成了架构设计、软件仿真验证及硬件实现。FPGA实现UDP协议栈的引入,加速了网络数据处理能力,提高了开发效率,降低了开发成本,很好地提高了声纳系统中数据传输速率和系统性能。

研究 设计 数据传输 协议 信号处理 UDP 声纳 相关文章:

- 基于TD-LTE的移动互联网研究(03-01)

- RFID在Rifidi中的仿真研究(06-14)

- 高频和微波功率基准及其应用研究(04-12)

- 基于RFID技术的后方仓库管理系统研究(08-14)

- HSDPA无线网络合/分载频规划方案的研究(06-13)

- MACH 2系统TDM通信接口的研究(05-20)