基于SOPC的脑电信号实时处理

on总线支持多个总线主外设,允许在单个总线事务中在外设之间传输多个数据单元。这一多主设备结构为构建SOPC系统提供了极大的灵活性,并且能够适应高带宽的外设。

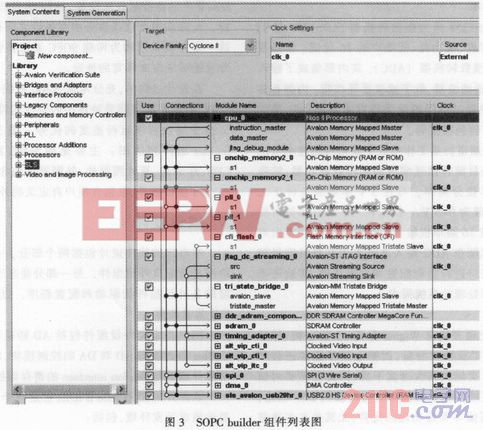

在设计过程中,充分考虑SOPC系统的特色,充分发挥了SOPC系统在数字信号处理中的并行运算优势和NiosⅡ自定义指令加快程序运行速度的优势。图3为本系统的SOPCbuilder组件列表图:主要是用SOPC Builder选取合适的CPU、存储器、及外围器件,外围器件包含系统自带的如定时器,SPI接口核等,也包含用户自定义的外设组件(AD,DA)。

3 软件设计

本系统的软件设计包括两个部分,一部分是基于Verilog的用户自定义外设组件,另一部分是基于NiosⅡIDE开发环境的各外设组件的驱动和配置程序,以及处理脑电信号的FFT算法程序。

用户自定义外设组件包括AD转换和DA转换模块,用Verilog语言编写AD和DA的控制模块,编译、综合后实现其功能并留下与Avalon interface的寄存器接口。

软件开发使用NiosⅡIDE,它是一个基于Eclipse IDE构架的集成开发环境,包括:

1)GNU开发工具(标准GCC编译器、连接器、汇编器和makefile工具等);

2)基于GDB的调试器,包括软件仿真和硬件调试;

3)提供用户一个硬件抽象层HAI。(Hardware Abstraction.Iayer);

4)提供嵌入式操作系统MicroC/OS一Ⅱ和LwlCP/IP协议栈的支持:

5)提供帮助用户快速入门的软件模板;

6)提供Flash下载支持(Flash。Programmer和QuartusⅡProgrammer)。

NiosⅡIDE可以完成NiosⅡ处理器系统的所有软件开发任务。SOPC Builder生成系统后,可以直接使用NiosⅡIDE开始设计C应用程序代码。Altera提供外设驱动程序和硬件抽象层(HAL),使用户能够快速编写与低级硬件细节无关的NiosⅡ程序。除了应用代码,用户还可以在NiosⅡIDE工程中设计和重新使用定制库。

基于C编写的算法程序是脑电信号数字处理的核心程序。该程序包括6个相关文件,分别是math.h,register.h,LF2407.CMD.RIS2X X.UB,process.c和evectors.asm。其中需要用到的数学公式库文件是math.h,CPI_I内部的寄存器及其相关定义文件是re面ster.h,连接命令文件是I~2407.CMD,指示编译器如何进行程序空间和数据空间的分配,系统提供RTS2XX.UB库文件,向量表文件cvectors.asm定义所需的复位和中断向量,process.c主要是完成用户期望的功能,是整个程序的核心部分。

FFT部分算法如下:

相关算法的说明:

1)采样频率Fs根据实际情况调整,仿真时为1 000 Hz;

2)快速傅里叶变换的计算公式为:

N是傅里叶变换的点数,此处为1 024点。

3)由于只计算相对功率,故在计算功率时没有除点数N;

4)本计算的步长取1 ms,将与采样频率对应,给计算带来方便。

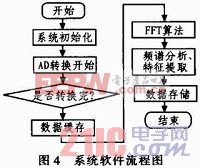

系统软件流程图如图4所示。

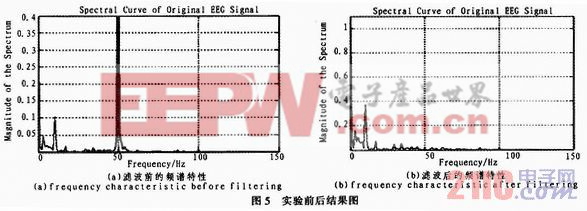

脑电信号是一种低频且极其微弱的信号,一般为5~1 000μV。脑电信号的采集又常常伴随着很大的噪声干扰,尤其是50 Hz的工频干扰。实验结果如图5所示。

经实验结果分析,本设计可以有效完成对脑电信号的去噪及滤除50 Hz的工频干扰,并能精确提取脑电信号的特征,为脑电信号的进一步研究做准备。

5 结束语

本设计的硬件实现都是在SOPC Builder环境下完成的,SOPC Builder提供的图形化系统架构平台极为方便地给设计人员提供了系统构建的优越性。SOPC Builder采用软件搭建硬件系统的方法,突破了硬件系统难裁剪,不易升级,开发周期长,维护困难等诸多缺陷。而且SOPC Builder可根据搭建的硬件系统自动生成对应的代码,可使各部件通过Avalon总线有序的连接和工作,将设计人员解放到系统框架的总体设计和用户程序的设计,大大地促进了开发效率,缩短了开发流程。此外SOPC中也极为方便的为设计人员提供了加入自己设计的组建和自己定制的指令的功能,这样可使开发人员可以通过自己定制的指令更加高效地完成设计。SOPC系统具有在硬件的可重构与可重配置,这是FPGA在硬件开发过程中独一无二的特点。

- 揭秘高主频智能手机的真实性能(04-23)

- SAW RFID阅读器的信号处理电路设计 (08-12)

- 英特尔再出手机挑战苹果(04-16)

- EDA环境衔接测量软件(06-25)

- 数字无线电前端策略为小型蜂窝基站带来改变(09-24)

- 红米Note开箱及拆解欣赏:5.5寸8核处理器(04-11)