基于VerilogHDL语言的FIR数字滤波器设计与实现

随着现场可编程门阵列的广泛应用,对其进行灵活的重新配置的研究也越来越多。目前绝大多数FPGA都是基于查找表LUT(Look UP Table)的技术,采用SRAM工艺生产。这种工艺的FPGA有两层结构,上层为配置存储器,下层是硬件逻辑层。通过上层配置信息控制硬件层门电路的通断,改变芯片内基本逻辑块的布线,从而形成特定的功能。这种架构为动态重构技术实现提供了可能。一个FPGA大型数字系统总是由很多功能模块组合而成,这样各个系统模块的激活状态就可能在时间轴上产生分离,时间上分离的模块就可以共用一个硬件逻辑区,根据需要对这个逻辑区动态地改变配置,实现不同的功能,这就是局部动态重构[1]。FPGA的动态重构使其应用更加灵活,减少了硬件的资源消耗,缩短了开发周期。但是对一些特殊场合,如深海数据采集或机器人野外勘探,开发者可以为某个系统模块设计几个功能,设备在自主运行过程中根据需要选择相应的配置数据进行配置。如果遇到特殊环境,事先设计的功能有可能不适合工作要求,需要增加新的功能。在目前硬件进化技术还无法进行实际应用的情况下,本文设计了一种远程动态重构的系统来解决上述问题。

1 远程动态重构系统的结构

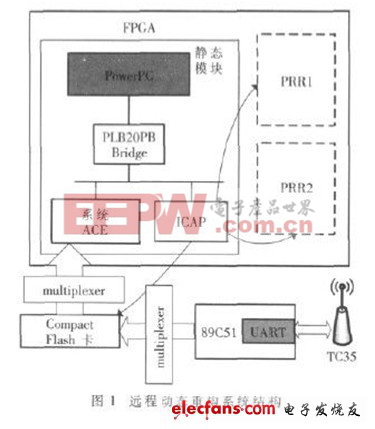

远程动态重构系统有PowerPC处理器和89C54微控制器两个核心。VirtexII-Pro FPGA内部集成有2个PowerPC405嵌入式处理器[2],本文系统使用其中一个,实现对动态重构进行控制和调配。FPGA内部用于对局部重构区域PRR进行重新配置的硬件模块有3个,分别是嵌入式内核PowerPC、系统高级配置环境System ACE和内部配置访问通道ICAP。System ACE是一种在系统编程的高级配置解决方案,它提供CF(Compact Flash)、MPU和Test JTAG等多个接口,本系统采用CF卡作为配置数据的来源,可以更方便地改变和存储配置数据。ICAP的主要作用就是按照特定时序将配置数据重新配置到PRR中[3]。

远程数据传输通过外接控制器89C54完成,一方面控制器要通过UART接口接收GSM模块TC35传来的数据;另一方面要把接收到的配置数据写入CF卡中,以供FPGA系统读取。

System ACE和89C54控制器共用CF卡的控制接口。为避免互相影响,本系使用多路复用器将CF卡端口做分时复用处理,即配置过程中与System ACE连接,而数据传输存储过程中与89C54进行连接。远程动态重构系统结构如图1所示。

2 远程动态重构的本地准备

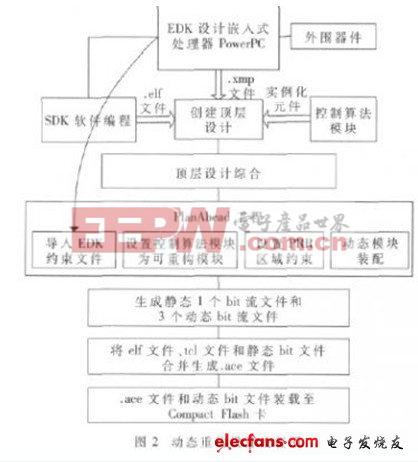

以机械手臂的控制为例,采用PID控制、模糊控制和备用三种控制方案,每个控制算法经过验证综合生成独立的bit流模块。这三个模块共用一个可重构的区域PRregion,根据具体情况,选用最适合的算法模块,动态地配置重构区域来控制机械手臂,其他静态逻辑区域则仍然正常运行。这样不仅提高了系统的灵活性,而且节省了配置时间、减少了不必要的消耗。FPGA的设计流程一般包括设计、仿真、综合、实现过程,本文根据系统自身结构提出如图2所示的设计流程。

FPGA重构系统综合使用EDK(Embedded Development Kit)、ISE和PlanAhead多种工具平台,采用分层化设计,以简化设计过程。其过程如下:

(1)利用嵌入式开发工具EDK设计一个基于PowerPC405的嵌入式控制系统[4],添加SystemACE_CompactFlash外设以支持从CF卡配置FPGA;添加IP核opb_hwicap以支持嵌入式内核通过ICAP读取配置数据动态地配置FPGA。

(2)EDK包含有软件开发工具SDK,因此利用SDK对PowerPC405进行软件编程和调试,最终生成应用程序二进制executable.elf文件;利用EDK外设创建向导,创建多个控制算法IP模块,在各自的VHDL文件中编写相应的算法;使用ISE工具对多个算法模块进行综合、创建顶层模块、实例化嵌入式系统和算法模块。综合产生top网表文件。

(3)创建PlanAhead工程,使用以上产生的网表文件和约束文件进行布局布线。其中最重要的是将算法模块设置为可重构模块,对其进行严格的区域约束[5],其约束代码如下:

AREA_GROUP “AL_PRregion” RANGE = SLICE_(minX)(minY):SLICE_(maxX)(maxY)

AREA_GROUP “AL_PRregion” RANGE = RAMB16_(minX)(minY):RAMB16(maxX)(maxY)

在PlanAhead工具中可以通过可视化方法进行区域约束,既直观又简单。可重构模块在运行过程中如果需要实现不同的控制算法,则需要在重构区中添加所有算法模块综合生成的网表文件、使用PR Assemble命令生成多个不同的算法bit流文件。除了动态bit流文件外,PlanAhead还会产生一个静态完整的bit流文件static_full.bit。可执行以下两个命令生成ace配置文件:

(1)data2mem -bm implementation/system_

滤波器 设计 实现 数字 FIR VerilogHDL 语言 基于 相关文章:

- 超导滤波器在TD-SCDMA基站等网络优化中的作用(03-11)

- 低通滤波器实例(04-23)

- 基于ispPAC的滤波器设计(08-11)

- 多层压敏电阻阵列的滤波连接器设计(06-21)

- 一种超低成本宽带中间阻抗转换器设计(11-24)

- 超导滤波器在TD-SCDMA基站等网优中作用(03-12)