模块化结构在便携式设备设计中的应用分析

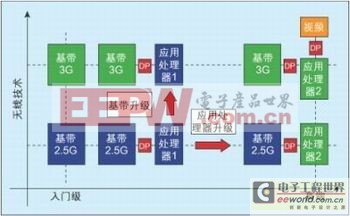

图3:采用模块化架构战略的手机系统。

在功率方面,Cypress的MoBL的低泄漏技术使双端口的待机功耗在1.8V时可低至3.6uW。由于市场上充斥各种基带处理器及其他处理器,它还支持多种I/O电压(1.8V、2.5V及3V)。

此外,随着对无线系统的带宽要求在不断增加。无线系统现在还要求能支持数据速率高达11Mbps的802.11b等非蜂窝技术。一些处理器上可用的标准低速率串行互连,通常难以提供所需的带宽,而Cypress MoBL双端口则能在x16总线上提供执行时间为35ns的快速访问,吞吐量高达400Mbps,超过3G、WiFi或视频广播所需的数据速率。

小占位面积则是另一项要求,Cypress MoBL双端口可以裸片提供,或采用小型6×6mm 0.5mm间距BGA封装。

在功能方面,Cypress MoBL双端口可与任何其他Cypress异步双端口相媲美。当两个端口试图同时访问同一存储器空间时,即会给出“忙”信号,以提供内建仲裁。其邮箱功能可使两个处理器只需简单地写入具体位置即可互相发送中断信号,这可用来向其他处理器发送数据可下载的信号。

手机系统设计者希望能减少GPIO引脚的数量,这些引脚用来驱动诸如读某些外部DIP开关或点亮LED等极为简单的功能。Cypress MoBL双端口通过将输入读寄存器及输出驱动寄存器合并在其特性中而能使上述某些信号从外部抵达处理器。输入读寄存器(IRR)将两个外部二进制器件(如DIP开关)的状态捕获至特定存储器空间中。只需简单地读双端口,任何一个处理器都能监视这两个器件的状态。输出驱动寄存器(ODR)可驱动多达5个中断信号,这使得任何一个处理器都能通过只在双端口特定位置上写数据来控制多达5个外部器件。

本文小结

为保持竞争力,便携式设备OEM们现在采用模块化设计战略,以使其能迅速进行平台升级并能缩短新手机的面市时间。双端口通过提供高吞吐量及存储器映射互连使这种战略的实现成为可能。它允许创建可单独演进并通过其存储器接口来相互通信的多个子系统。为响应这一新的需求,Cypress公司设计了专用于此类应用的新型MoBL双端口,并使其成为一种低功率双端口器件。

- 浅析ICS直放站的应用(08-07)

- 基站应用中功放的分立控制和集成控制(04-25)

- 电子标签:RFID技术应用与七大特点(05-12)

- 射频/微波器件面向太空应用可靠性是关键(12-17)

- 以软件为核心的无线测试平台的设计(03-18)

- 高频和微波功率基准及其应用研究(04-12)