基于FPGA的嵌入式串行千兆以太网设计

本系统使用时钟生成器IP核生成系统各模块工作时所需时钟。该IP核模块的输入时钟为FPGA全局时钟引脚输入的100 MHz时钟,经过相应的倍频,生成400 MHz的PowerPC440工作时钟,生成200 MHz的DDR Il工作时钟以及125 MHz的Ethernet MAC工作时钟。

在各模块添加及连接结束后,需添加UCF约束文件,包括FPGA引脚约束和相应的时序约束等,并对XPS自动生成的微处理器硬件规范MHS文件进行相应的修改,对系统进行适当的优化。生成的系统在综合、布局、布线无误后生成最终的.bit文件,准备下载到电路板上。

3 嵌入式系统软件设计

本系统软件部分需实现TCP/IP网络协议,TCP/IP协议模型包括应用层、传输层、网络层和网络接口层。网络接口层分为PHY层和MAC层两部分。其中,PHY层由外部PHY芯片88E1111实现,MAC层由Xilinx公司的Hard Ethernet MAC IP核实现,并作为整个Power-PC系统硬件的一部分在FPGA的内部实现。

网络层和传输层主要采用LwIP协议模块编写相应的软件代码。LwIP同时支持服务器模式和客户端模式,提供RAW和Socket两种API。它的特点是在保持TCP/IP协议主要功能的情况下,减少对RAW的使用,使得LwIP在各类高档嵌入式系统开发中得到广泛的应用。本设计选择Xili nx公司的精简嵌入式操作系统Xilkernel,用于更好地管理系统资源。Xilkernel能与EDK形成的硬件系统紧密结合,是一种可定制的简单高效系统。Xilkernel系统的配置可以在开发环境SDK中进行手动设置。本设计中运用LwIP协议模块编写运行在Xilkernel操作系统上的应用软件,实现了Web Server(网页服务)、FTP(FileTransfer Protocl)、Telnet远程登录服务、iperf应用等功能。下面以网页服务程序、iperf服务器和客户端程序为例对软件设计流程进行说明。

具体流程描述如下:

①在Xilkernel系统的静态启动线程main_thread()中,初始化网络协议和文件系统。

②调用线程生成函数sys_thread_new()生成并启动线程1。

③在线程1中设置电路板硬件的MAC地址、网关、IP地址和子网掩码等参数,并初始化网络接口。具体设置方式如下:MAC地址为00;0a:35;00;01;02;IP4地址为192.168.1.10;IP4地址掩码为255.255.255.0;IP4地址网关为192.168.1.1。

④初始化一个Socket,将它与IP地址和端口号绑定,然后开始监听网络,一旦监听到网络请求,再由函数sys_thread_new()生成一个线程2去响应,用于缓存接收到的数据包。然后,通过函数launch_app_threads()判断监听到的网络请求属于哪种类型,并由函数sys_thread_ new()生成相应的线程3去处理。

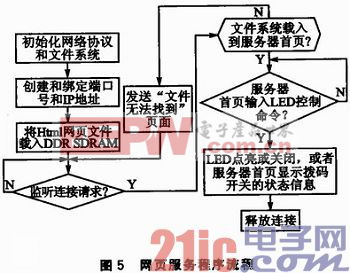

如果是网络服务请求,则将网页文件输出到PC机上,并接收PC机传输的控制数据信息,其程序流程如图5所示。如果是iperf应用请求,则发送或接收相应的数据完成对请求的响应。

网页服务程序运行前需在FPGA外部的DDR中建立文件系统,将用于控制的相关网页文件保存在该文件系统中。系统在运行时,访问预设的IP地址,会将相关网页文件传输到远端控制电脑上,并通过网页中的超链接命令脚本将预设的控制信息传送给PowerPC处理器,用以控制电路板上的LED灯亮灭,或者读取电路板上拨码开关的状态值并在服务器首页上显示。

本设计中采用iperf网络测试软件对其性能进行测试。采用9 000字节巨帧可以实现高达490 Mbps的传输速率。

结语

本文成功使用Virtex-5 FX70t芯片实现串行千兆以太网系统,并通过网页服务程序对其功能加以验证。本系统在硬件电路设计阶段具有I/O端口数目少、便于PCB布线,以及信号完整性容易保证等优点。通过iperf网络测试软件对其传输速率进行测试,其结果达到高速数据传输的要求。

千兆以太网 FPGA SGMII PowerPCA40 相关文章:

- 基于FPGA的短波通信接收机(11-19)

- FPGA的低功耗设计(07-06)

- EDA环境衔接测量软件(06-25)

- Altera 28nm FPGA助力NEC提升LTE基站性能(11-19)

- 基于FPGA的BPSK信号载频估计单元设计(09-02)

- FPGA推动5G异构无线网络(09-28)