基于GPS的恒温晶振频率校准系统的设计与实现

的改变需有一定的响应时间,快速调整压控端的电压会产生过调现象,频率稳定度不佳。

为进一步提高晶振频率的精度与稳定性,结合恒温晶振短期稳定度高的特点,在数字鉴相器模块中,以GPS的1PPS信号为基准,测量1PPS与恒温晶振分频出的1Hz信号的相位差。依据GPS没有累积误差的优点,在环路滤波器模块中采用滑动平均滤波法来降低GPS秒脉冲对测量带来的干扰,设计FIFO存储器来配合计算出最近200 s的平均相位差,通过不断对比短时的相位差及长时的平均相位差,分析相位差的长期与短期变化动态,实时调节恒温晶振的控制电压,保证晶振输出稳定且准确的10 MHz时钟信号。晶振频率调整的过程如图3所示,此方法简单实用,可有效抑制1PPS抖动对晶振造成的影响。

2.2 电路设计

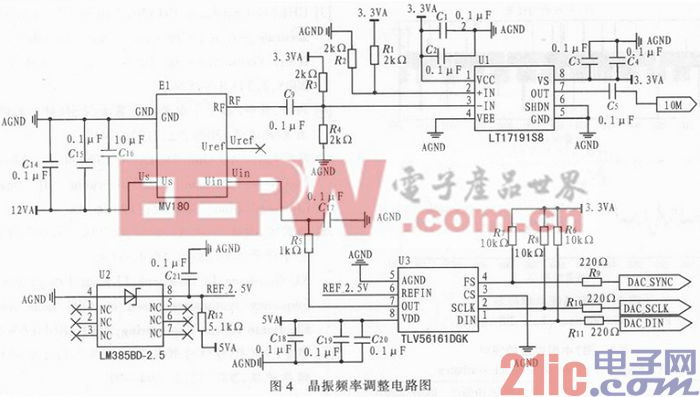

D/A芯片选用TI公司TLV5616,它是低功耗单片12位串行数模转换器,分辨率为4096,该芯片采用三线制(SCLK、SYNC、DIN)串行接口,SCLK方波信号为下降沿时,TLV5616读取DIN的电平信号,转化成相应的电压送往恒温晶振,用于晶振的微调,晶振频率调整硬件电路如图4所示。

2.3 授时功能

在许多现实的应用中需要毫秒、微秒、纳秒等这些更小的时间单位量,但是GPS接收机一般只能提供最小时间单位为秒的UTC时间,本系统在GPS基础上设计了授时功能。

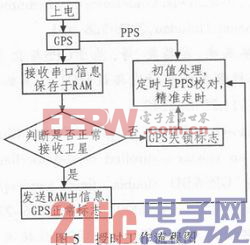

授时工作流程如图5所示,系统在FPGA中设计串口数据模块来接收GPs的SD01管脚发出的GPRMC格式数据,并将其存放在FPGA内部的双口RAM中,通过串口数据模块及数字鉴相器模块可以判断GPS接收机是否正常工作。若识别出准确的UTC时间和1PPS信号后,授时模块迅速从RAM中提取最新时间数据进行处理,得到初始时间值,当下一个1PPS上升沿到来后,系统在初值的基础上开始完全依靠高稳恒温晶振自行走时,并每隔5秒与准确的1PPS信号进行校对,如果发现本系统的时间与1PPS不同步,那么系统时间将会短暂停滞或快速跳进,达到与1PPS同步,保证时间信息输出的连续性与准确性;若GPS接收机非正常输出1PPS信号,则不进行校对,直到1PPS正常后再恢复校对功能。

3 实验结果

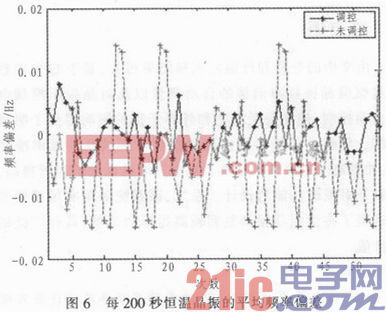

在卫星信号正确接收的情况下,系统可以在短时间内把恒温晶振的频率校准到较高的准确度与稳定度上。实验结果表明,恒温晶振被调节后可以输出更准确的10MHz信号,误差小于0.01 Hz,频率的精度与长期稳定性都得到明显改善。1PPS信号没有累计误差,在连续不重复的201个1PPS上升沿之间,即以200 s作为闸门时间,测出恒温晶振MV180在调控与未调控状态时,每200 s的平均频率偏差,图6为部分实际测试图,实线和虚线分别代表恒温晶振在调控与未经调控状态的测试结果,其中实线部分的平均频率偏差是-7.41x10-5Hz,均方差为3.10x10-3Hz。

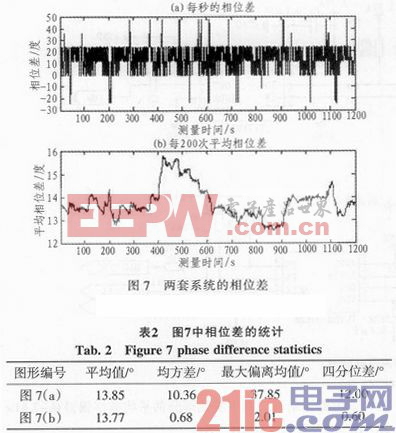

依照文中方案设计两套完全独立的系统,以其中一套系统的恒温晶振的时钟信号为基准,每秒与另一套系统的恒温晶振的时钟信号对比一次,相位差用300 MHz的时钟进行量化,测量分辨力为3.3 ns,部分测试结果如图7所示。图7(a)显示每秒测得的相位差;由于存在测量误差,因此采用滑动平均滤波的方法,在每秒测量两套系统相位差的同时,计算出最近200次的平均相位差,如图7(b)所示。表2对图7的实际测量数据进行统计,7(b)中的均方差是0.68度,四分位差为O.60度,说明两套独立系统的频率一致性很高,具有良好的稳定度。

恒温晶振经过校准后的频率偏差小于0.01 Hz,在1PPS准确输出时,累加1PPS具有的100 ns误差,授时模块输出的时间信息误差小于105 ns。当GPS接收机未正常工作时,由于恒温晶振前期经过频率校准和自身较高的稳定度,在一定时间内依然可以保证高精度的授时功能。

4 结束语

由文中的分析和详细的实验结果可知,基于GPS的秒信号对恒温晶振频率偏移的自动测量以及对晶振压控端电压的自动控制,使晶振受老化和外界干扰的影响得到了明显的抑制,能够在较短时间内将晶振校准到较高的频率准确度上,并提高长时间的稳定性。晶振频率准确度的显著提高,也有利于对授时功能的设计。总之,该系统采用实用简便的方法达到了将恒温晶振调整到较高指标的目的,具有广泛的应用价值。

- 基于FPGA的短波通信接收机(11-19)

- FPGA的低功耗设计(07-06)

- EDA环境衔接测量软件(06-25)

- Altera 28nm FPGA助力NEC提升LTE基站性能(11-19)

- 基于FPGA的BPSK信号载频估计单元设计(09-02)

- FPGA推动5G异构无线网络(09-28)