一种基于DSP与FPGA的高速通信接口设计方案

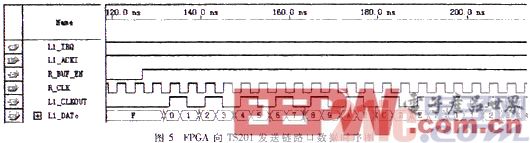

_EN是读发送缓存使能信号;链路口时钟L1_CLKOUT是以读缓存时钟R_CLK下降沿的二次分频,对应从缓存中读出的4bit链路口数据L1_DA-To。注意这里读缓存及时钟分频时会有纳秒级的延迟。

3 DSP的相应设置

TS101和TS201的链路口都配置了控制寄存器(LCTLX)和状态奇存器(LSTATx)两组寄存器。LCTLx用来控制链路口的传输,LSTATx用来通知链路口的工作状态。TS101链路口时钟频率可以是核时钟的8、4、3或2分频,通过设置LCTLx中的SPD位米完成,本文设计将SPD位置000,即为核时钟8分频。由于TS201的接收发送通道独立,所以其控制寄存器分为接收控制寄存器(LRCTLx)和发送控制寄存器 (LTCTLx)。TS101链路口发送时钟频率可以与核时钟相同或为其4、2、1.5分频,通过设置LTCTLx中SPD位来完成。本文设计将SPD位置100,即为核时钟4分频,并将LRCTLx/LTCTLx中(接TDSIZE位置1,设置成4bit传输方式。如果BCMP#信号悬空,注意一定要将 LRCTLx巾RBCMPE位置0。

有两种方法启动DSP的链路口DMA传输:利用链路中断和利用DSP的四个外部中断(IRQ0~IRQ3)。两种中断方式都需要在中断服务程序中对 DMA的TCB寄存器进行配置来启动链路口的接收DMA通道。鉴于外部中断的优先级高于链路口中断,可以避免数据丢失,本文设计的通信方式均以外部中断方式通知DSP接收数据。在DMA的TCB寄存器配置过程中,为了保证程序不被其他中断打断,可以在中断服务程序开始时就把所有其他中断屏蔽掉,存中断服务程序返回之前再把屏蔽掉的中断位还原。

本文对TigerSHARC系列的两种典型DSP芯片的链路口进行了分析和比较,并给出了FPGA与这两种DSP芯片进行链路口通倍的具体方法。在 FPGA内部实现了DSP链路口的设计,同时给出了DSP进行链路口通信的具体设置方法。由于实时处理中数据的重发会严重影响处理的实时性,故本文的链路口通信设计没有对所传输的数据进行校验。本文给出的基于FPGA路口设计具有很强的通用性,可以应用于基于TS101/TS201的多种应用系统中,提高系统内部的通信能力;也可用于板间DSP的数据传输,提高系统外部的通信能力。

- 跳频电台射频前端电路设计攻略(04-15)

- DSP硬件设计的几个注意事项(06-04)

- LEON2应用于DCPU的FPGA仿真(05-11)

- 数字对讲机工作原理及数字对讲机关键器件的构成(07-28)

- 浅析雷达技术新应用(08-23)

- 基于DSP的机载选呼解码器设计 (03-29)