采用两级电路实现的地址变化探测器

时间:06-12

来源:互联网

点击:

引言

静态随机存取存储器(SRAM)由于其优越的性能(速度高、功耗低),被广泛应用于作为高速缓存的最大量的挥发性存储器。 近年来随着便携式数字电子产品的日益普及,SRAM速度高、功耗低的要求也越来越强烈,这亦成为SRAM未来发展的主要趋势。

提高速度、降低功耗是SRAM设计的主要目标。提高其性能的关键是设计好单元和读出灵敏放大器,此外在总体结构设计上也采取了许多措施改善SRAM的性能。本文提出一种新型地址变化探测电路来降低SRAM的维持功耗和提高工作速度,更提高了SRAM的抗噪声、抗干扰能力。

1 传统地址变化探测器电路

SRAM有异步和同步之分,它们的结构和速度各异。对于异步SRAM为了降低SRAM的维持功耗和提高工作速度,设计了一种自定时方式,增加了一个地址变化探测器。当地址变化出现时,电路自动检测该地址总线上的任何变化。不需要任何外部的时序信号,可产生一个ATD信号,所有内部的时序操作(如启动译码器和灵敏放大器等)都来自内部产生的翻转信号,而不必等待同步时钟信号控制,从而提高了工作速度。这一方法的优点是使SRAM的存取时间接近或等于它的周期时间。 另外,译码器受ATD信号控制,在维持状态下使所有的字线都为低电平,这将消除维持状态下的列电流,进一步降低芯片的功耗。

图1为一个传统地址变化探测器电路。A0到An-1任何一个端口输入信号上的翻转都会引起ATi下降到低电平并持续一个时间,由此产生的脉冲作为存储器其余部分主要的时序参考。

传统地址变化探测电路在提高速度和降低功耗的优点是显而易见的,但是在大容量的SRAM的制造中,由于集成密度的增加,提高了因信号间的耦合而造成的噪声电平,同时对速度的更高要求也使得存储器的切换噪声也相应增加。尤其当PAD上有外部干扰信号影响时,将会改变ATD的脉宽,从而导致SRAM的读写错误。

传统地址变化探测电路在提高速度和降低功耗的优点是显而易见的,但是在大容量的SRAM的制造中,由于集成密度的增加,提高了因信号间的耦合而造成的噪声电平,同时对速度的更高要求也使得存储器的切换噪声也相应增加。尤其当PAD上有外部干扰信号影响时,将会改变ATD的脉宽,从而导致SRAM的读写错误。

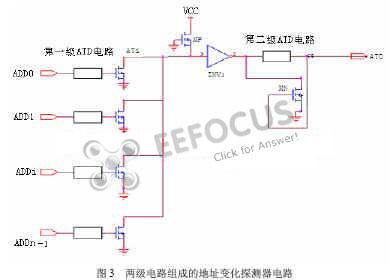

本文在传统地址变化探测电路的基础上,增加一级新型地址变化探测器电路,构成有两级电路组成的地址变化探测器电路,来提高SRAM的抗噪性。

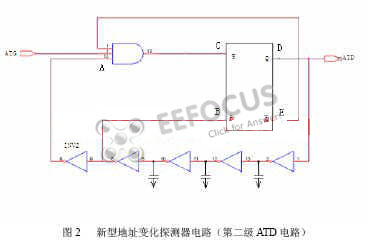

图2为新型地址变化探测器电路

新型地址变化探测器电路(图2)的工作原理如下:

1 ) 电路初始化

没有任何地址变化时,由上拉管MP将ATi 置为高电平,由反相器INV1,ATG置为低电平;通过三输入与门,C为低电平。

当C为低电平,B为高电平时,则由RS触发器,D为低电平,E为高电平;由延时链和反相器INV2,A为高电平,B为低电平;A、B、C、D、E处的电位将保持稳定状态。

当C为低电平,B为低电平时,若当RS触发器原状态D为低电平,E为高电平;由延时链和反相器INV2,A为高电平,B为低电平;A、B、C、D、E处的电位将保持稳定状态。

当C为低电平,B为低电平时,若当RS触发器原状态D为高电平,E为低电平;由延时链和反相器INV2,A为低电平,B为高电平;由RS触发器,E为高电平,D为低电平;再由由延时链和反相器INV2,A为高电平,B为低电平;A、B、C、D、E处的电位将保持稳定状态。

因此,当电路初始化后,A和E被置为高电平,B、C和D(ATD)被置为低电平。

2) 当任一地址ADDi有变化时,第一级电路将ATi置为低电平。在第二级电路中,当任一ATi为低电平时,则ATG将为高电平,C也将为高电平。当C为高电平时,即将RS触发器S端置为高电平,所以Q端为高电平,即D(ATD)为高电平。同时E为低电平,通过反馈环使C翻转为低电平,此时B为初态低电平,因此触发器保持状态。当D点高电平经过延时反相器链将B置为高电平,D翻转为低电平,从而产生一个完整的ATD信号。

3) 延时反相器链中反相器宽长比尺寸的调整将决定B点的瞬态电压,这也是决定ATD信号脉宽的关键。

3 仿真结果

图4是用HSPICE对采用两级电路实现的地址变化探测器进行仿真的波形。由此波形图可以看出,当地址端ADD0有地址信号输入时,经过第一级ATD电路(传统地址变化探测器电路),ATG将会产生需要的脉冲信号;而当地址端ADD1有不期望的干扰信号输入时 ,经过第一级ATD电路(传统地址变化探测器电路),ATG则会产生不需要的脉冲信号。然而经过第二级新型地址变化探测器电路,不期望的干扰信号被拒绝,输出需要的ATD信号。

由ATG和ATD的波形可以看出,两级电路实现的地址变化探测器虽然提高了抗干扰能力,但是,产生了一定的时间延迟。所以,本电路抗干扰能力的提高,导致了SRAM的存取速度降低。

静态随机存取存储器(SRAM)由于其优越的性能(速度高、功耗低),被广泛应用于作为高速缓存的最大量的挥发性存储器。 近年来随着便携式数字电子产品的日益普及,SRAM速度高、功耗低的要求也越来越强烈,这亦成为SRAM未来发展的主要趋势。

提高速度、降低功耗是SRAM设计的主要目标。提高其性能的关键是设计好单元和读出灵敏放大器,此外在总体结构设计上也采取了许多措施改善SRAM的性能。本文提出一种新型地址变化探测电路来降低SRAM的维持功耗和提高工作速度,更提高了SRAM的抗噪声、抗干扰能力。

1 传统地址变化探测器电路

SRAM有异步和同步之分,它们的结构和速度各异。对于异步SRAM为了降低SRAM的维持功耗和提高工作速度,设计了一种自定时方式,增加了一个地址变化探测器。当地址变化出现时,电路自动检测该地址总线上的任何变化。不需要任何外部的时序信号,可产生一个ATD信号,所有内部的时序操作(如启动译码器和灵敏放大器等)都来自内部产生的翻转信号,而不必等待同步时钟信号控制,从而提高了工作速度。这一方法的优点是使SRAM的存取时间接近或等于它的周期时间。 另外,译码器受ATD信号控制,在维持状态下使所有的字线都为低电平,这将消除维持状态下的列电流,进一步降低芯片的功耗。

图1为一个传统地址变化探测器电路。A0到An-1任何一个端口输入信号上的翻转都会引起ATi下降到低电平并持续一个时间,由此产生的脉冲作为存储器其余部分主要的时序参考。

传统地址变化探测电路在提高速度和降低功耗的优点是显而易见的,但是在大容量的SRAM的制造中,由于集成密度的增加,提高了因信号间的耦合而造成的噪声电平,同时对速度的更高要求也使得存储器的切换噪声也相应增加。尤其当PAD上有外部干扰信号影响时,将会改变ATD的脉宽,从而导致SRAM的读写错误。

传统地址变化探测电路在提高速度和降低功耗的优点是显而易见的,但是在大容量的SRAM的制造中,由于集成密度的增加,提高了因信号间的耦合而造成的噪声电平,同时对速度的更高要求也使得存储器的切换噪声也相应增加。尤其当PAD上有外部干扰信号影响时,将会改变ATD的脉宽,从而导致SRAM的读写错误。

本文在传统地址变化探测电路的基础上,增加一级新型地址变化探测器电路,构成有两级电路组成的地址变化探测器电路,来提高SRAM的抗噪性。

图2为新型地址变化探测器电路

新型地址变化探测器电路(图2)的工作原理如下:

1 ) 电路初始化

没有任何地址变化时,由上拉管MP将ATi 置为高电平,由反相器INV1,ATG置为低电平;通过三输入与门,C为低电平。

当C为低电平,B为高电平时,则由RS触发器,D为低电平,E为高电平;由延时链和反相器INV2,A为高电平,B为低电平;A、B、C、D、E处的电位将保持稳定状态。

当C为低电平,B为低电平时,若当RS触发器原状态D为低电平,E为高电平;由延时链和反相器INV2,A为高电平,B为低电平;A、B、C、D、E处的电位将保持稳定状态。

当C为低电平,B为低电平时,若当RS触发器原状态D为高电平,E为低电平;由延时链和反相器INV2,A为低电平,B为高电平;由RS触发器,E为高电平,D为低电平;再由由延时链和反相器INV2,A为高电平,B为低电平;A、B、C、D、E处的电位将保持稳定状态。

因此,当电路初始化后,A和E被置为高电平,B、C和D(ATD)被置为低电平。

2) 当任一地址ADDi有变化时,第一级电路将ATi置为低电平。在第二级电路中,当任一ATi为低电平时,则ATG将为高电平,C也将为高电平。当C为高电平时,即将RS触发器S端置为高电平,所以Q端为高电平,即D(ATD)为高电平。同时E为低电平,通过反馈环使C翻转为低电平,此时B为初态低电平,因此触发器保持状态。当D点高电平经过延时反相器链将B置为高电平,D翻转为低电平,从而产生一个完整的ATD信号。

3) 延时反相器链中反相器宽长比尺寸的调整将决定B点的瞬态电压,这也是决定ATD信号脉宽的关键。

3 仿真结果

图4是用HSPICE对采用两级电路实现的地址变化探测器进行仿真的波形。由此波形图可以看出,当地址端ADD0有地址信号输入时,经过第一级ATD电路(传统地址变化探测器电路),ATG将会产生需要的脉冲信号;而当地址端ADD1有不期望的干扰信号输入时 ,经过第一级ATD电路(传统地址变化探测器电路),ATG则会产生不需要的脉冲信号。然而经过第二级新型地址变化探测器电路,不期望的干扰信号被拒绝,输出需要的ATD信号。

由ATG和ATD的波形可以看出,两级电路实现的地址变化探测器虽然提高了抗干扰能力,但是,产生了一定的时间延迟。所以,本电路抗干扰能力的提高,导致了SRAM的存取速度降低。

- 在系统设计中的如何选择半导体器件:ASIC,还是FPGA?(05-29)

- 如何降低MIPS CPU 50%的动态功耗(05-31)

- 使用QDR-IV设计高性能网络系统之二(06-08)

- 相变存储器(PCM)技术基础(06-12)

- 基于web服务器的可重构硬件测控平台设计方案(06-08)

- XPM存储器RFID高频接口设计简介(09-02)