连续时间Sigma-Delta模/数转换器(下)

在配备有CT反馈的CTΣΔ模/数转换器中,由于放大器的输出永远不会即时开关其输出电压,因此没有必要稳定输出,从而可放宽放大器在速度上的限制。虽然很难进行一个绝对的比较,但采样输入模/数转换器的SC天性使得它比起CTΣΔ更需要使用较高速度的放大器,因此其功耗比起流水线或DTSD模/数转换器的更大。此外,CTΣΔ模/数转换器并不要求迅速稳定下来,这也使它在相同的技术下,比起传统的DTSD模/数转换器的采样率更高。

对于任何系统尤其是便携设备来说,低功耗和高能源效率的操作都是极之重要的,因为降低功耗可以延长电池的寿命和减轻散发出来的热量。手持超声波医疗系统等应用尤其看重这一点。ADC12EU050采用1.2V电源,非常适合应用在单电池供电的系统中。

抗混叠滤波

CTΣΔ模/数转换器架构消除了对输入滤波的严格要求,原因是它已具备有天生的抗混叠滤波能力。在ADC12EU050中,很多的抗混叠滤波器性能特性都建基于数字技术上,因而产生出很高的通带平整度和很陡斜的滚降 (高度有效的阶级)。

CTΣΔ的抗混叠性在于同时采用了SD调制器和CT电路。对于任何类型的SD模/数转换器来说(CT或DT),过采样和其后对调制器输出的抽取滤波均须使用一个非常陡斜的滚降低通滤波器,其中断频率要是模/数转换器输出率的二分一。相反,一个没有过采样的奈奎斯特率模/数转换器则必须在模/数转换器之前加入一个高阶的外部低通滤波器,以防止有与输出采样率倍数相近的信号混叠在频带内。关于这点,我们在上文中已讨论过流水线模/数转换器的输入滤波和采样时钟要求。

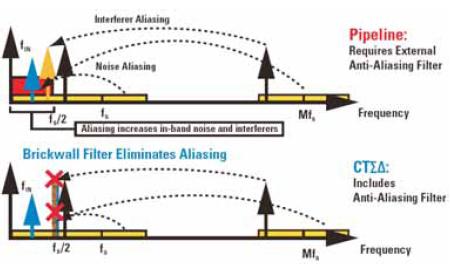

然而,除了上述的SD架构先天优点外,CT电路还有一个优点远胜DTSD模/数转换器。由于CTΣΔ模/数转换器是于前置环路滤波器的输出处采样,因此信号会于被采样前首先被环路的低通滤波器过滤,这便衰减了那些在调制器环路采样率(Mfs)附近并有可能混叠到频带内的信号。再者,由于这些混叠信号之后会在内部量化器的输入处被注入,噪声被环路的整形方或会与量化噪声的整形方式相同。这两种现象促使CTΣΔ除了在过采样和数字滤波能力上优于流水线设计外,它还能提供比DTSD更佳的抗混叠滤波能力。图4总结出CTΣΔ模/数转换器与流水线模/数转换器在抗混叠性能上的比较。

图4 CTSD和流水线模/数转换器的抗混叠性能

干扰混叠、噪声混叠、流水线(要求有外部抗混叠滤波器)、频率、混叠增加带内噪声和干扰、砖墙滤波器消除混叠、包括抗混叠滤波器、频率。这高效的先天抗混叠滤波能力大大降低或甚至免消除对外加抗混叠滤波器的要求。

即使如此,CTΣΔ的抗混叠性能也不应被过份夸大,因为抗混叠的要求是取决于不同的应用,而且它可能同时对设计复杂度、系统大小和成本构成一定的压力。正如之前讨论过,通过将采样率提升到所需输入带宽的两倍以上,便可放宽流水线或其它奈奎斯特率模/数转换器对抗混叠的要求,但这会浪费带宽并降低系统的整体能效。一个模拟抗混叠滤波器设计会存有陡斜的中断特性,因此要达到一个非常平整的通带是一项非常艰巨的任务,这要求高阶和高插入损耗的滤波器网络,因而必须增大信号路径中的增益以补偿该损耗。

通过消除采样输入模/数转换器所需的附加过采样,使得CTΣΔ能让系统设计人员使用差不多所有的转换器奈奎斯特带宽,从而大大改善电源效率。此外,由于可免除使用昂贵的外加抗混叠滤波器,使得ADC12EU050能降低对模/数转换器驱动器的需求,进一步简化了系统设计的复杂性和降低整体的成本和功耗。

低噪声并易于驱动的输入

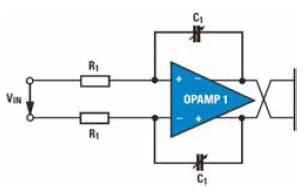

CTΣΔ模/数转换器的输入噪音比采样输入模.数转换器的输入噪音更低,这主要归功于内置电路的CT。在一个流水线或传统的DTSD采样输入模/数转换器中,其输入级均包含有一个通常较大的开关电容器,以用来削减模/数转换器的整体热噪声。驱动这个大的开关电容器并不容易,尤其对DTSD模/数转换器来说,因为它们的调制器是以输出数据率的几倍速度来进行采样。此外,来自这些输入的较大开关噪声可以耦合到系统,导致系统的整体性能下降。另外,可以施加到开关电容输入的输入电压也会因输入的采样开关之栅极源级电压而受到限制。与SC采样输入相反,CTΣΔ技术可展现出一个稳定的电阻性输入,正如图5中所示。

图5 CTSD模/数转换器输入的模型

由于CTΣΔ的输入没有被采样,所以无需使用开关电容器,而且输入也比较容量驱动,因此可使

转换器 CTΣΔ调制器 锁相环 采样时钟 NI 200806 相关文章:

- RS-232至RS-485RS-422接口的智能转换器(01-24)

- 同步降压转换器电路设计基础(01-01)

- 真有效值AC/DC转换器AD736及其在RMS仪表电路中的应用(02-16)

- 满足FPGA电源设计需求的DC/DC转换器(02-15)

- 开关DC-DC转换器的EMI方案(04-29)

- 多媒体手机的电源管理方案(04-26)