高速ADC THS1041的钳位功能

利用钳位脉冲控制功能测试DC行为

钳位脉冲控制就是在Clamp引脚处施加一个脉冲信号以控制Clampout引脚的内部缓冲器接入。为了观察THS1041模拟输入端的DC行为,我们将一个脉冲信号而非一个DC信号施加到具有16kHz和6%占空比的Clamp引脚(请参见图2)。与之前的测试相类似,将去耦电源的1V固定DC电压施加到 Clampin,并将一个可变DC电压施加到AIN-。在这种情况下,在脉冲钳位期间,AIN+被内部缓冲器驱动至1V,并且当AIN-为1V时,在钳位脉冲间隔期间,电容器C2很好地保持了该电平。电容C2必须要足够大且钳位脉冲间隔要足够小以使AIN+端的DC电压与Clampin端的DC电压保持一致。但是,如果AIN-端的DC偏移与AIN+端的DC偏移设置的不一样,那么DC信号就出现失真。如前所述,当一个引脚或另一个引脚正在浮动时,模拟输入引脚处的DC电压就会发生漂移。利用钳位脉冲控制进行的测试进一步证明了这一表述。在将一个脉冲施加到Clamp引脚时,DC漂移表现为一个电压峰值,这一现象是通过图3所示的示波器观察到的。

该峰值周期性地出现在钳位脉冲频率时的AIN+端,且其幅度会随着模拟输入引脚间DC压差的增加而增加。测试数据显示,当Clampin被连接到一个1V电源且AIN-被连接到一个0.5V电源时,在钳位脉冲逻辑高电平和逻辑低电平期间AIN+端的DC测量值为1V。AIN+端的AC测量值为大约20mV的正峰值,并且会在钳位脉冲从低到高的转换时出现。当AIN-被连接到一个1.5V电源且Clampin仍然被连接到一个1V电源时,AIN+端的DC测量值为1V。AIN+端的DC测量值是一个大约为30mV的负峰值,并且会在钳位脉冲从低到高的转换时出现。当AIN–被连接到一个1V电源(与AIN+端的DC电压相等)时,就会出现该峰值且AIN+端的1VDC电压平滑稳定。

更多的测试显示,当钳位脉冲的占空比变高时,峰值就会变小。在Clampout引脚处添加一个电容器C3将会大大限制该峰值。

钳位脉冲控制条件下的THS1041AC性能

模拟输入端AIN+处的峰值会降低THS1041的AC性能(请参见图4和图5)。图4和图5均为在钳位脉冲控制和模拟输入引脚上不同DC电压条件时 THS1041的FFT图。该FFT图是由LabviewFFT程序根据HP1600逻辑分析器从THS1041EVM采集的数据生成的。EVM模拟输入端的测试信号为一个2.2-MHz的正弦波,振幅为–20dBFS(即低于ADC满量程20dB)。该测试信号由一个HP8644正弦波生成器生成,并通过一个板上变压器由THS1041SE输入端完成接收(本测试EVM板详尽的设置工作将在本文的后面讨论)。由HP8644触发的脉冲生成器将以 40MHz运行THS1041输入时钟。钳位脉冲由具有15.6kHz频率和50%占空比的脉冲生成器生成。

在时域中,峰值周期性地出现在图3所示的钳位脉冲频率上。在频率域中,峰值出现在FFT上的15.6kHz频率处(频率轴的低端)。当模拟输入引脚上的DC 压差为0.5V(AIN+为1V,而AIN–为0.5V)时,15.6kHz频率时的峰值为–67dBFS,这是FFT中最大的峰值(请参见图4)。该峰值要比FFT上的任何谐波都要高许多,并且有利于实现较低值的无杂散动态范围(SFDR)。当压差为0V(AIN+和AIN–均为1V)时,相同频率时的峰值为–82dBFS,提高了15-dB(请参见图5)。该峰值不但低于二阶和三阶谐波,而且还低于总谐波失真(THD)。

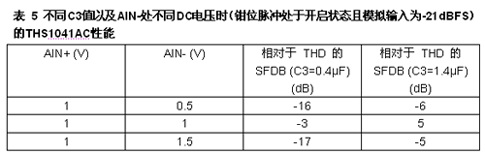

图 4和图5显示:随着AIN+和AIN–之间的DC压差增加到一定的水平,如果输入模拟信号小,SFDR则会下降并且会变得比THD更为糟糕。如果 Clampout处的去耦电容C3(请参见图2)不够大的话,尤为如此。在这些测试结果的基础上,我们利用Clampout处不同的去耦电容进行了进一步的测试。由于一个–21dBFS(低于THS10412V满量程输入21dB)模拟输入振幅、一个0.4μF的C3值以及AIN+和AIN–之间一个 0.5V的DC压差,SFDR比THD要低大约16dB。在相同C3值的情况下,当AIN+和AIN–之间的DC压差降至0V时SFDR要比THD低 3dB。如果C3被增加至1.4μF,那么包括SFDR、THD以及信噪比(SNR)在内的整体AC性能就会大大提高。因此,当AIN+和AIN–之间的 DC压差为0V时SFDR要比THD高大约5dB,且当AIN+和AIN–之间的DC压差为0.5V时SFDR要比THD低大约6dB。该测试数据如表5 所示。

该测试数据显示:AIN+和AIN–之间的DC压差不仅可导致模拟输入端的一个峰值,而且还会导致过早的输出饱和,从而降低最大的模拟输入振幅。例如,当 AIN+和AIN–之间的DC压差为0.5V时(AIN+为1V),最大模拟输入振幅就必须要低于满量程20dB以避免输出饱和。当AIN+和AIN–之间的DC压差为0.3V时(AIN+为1V),最大模

- 12位串行A/D转换器MAX187的应用(10-06)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- 12位串行A/D转换器的原理及应用开发(10-09)

- 在射击探测器中增加口径确定功能的简单电路(11-13)

- 一种折叠共源共栅运算放大器的设计(11-20)

- 深入解析:模拟前端模/数转换器的三种类型 (11-26)