CMOS图像传感器集成A/D转换器技术的研究

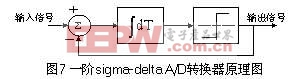

2.2.1逐次逼近型A/D转换器 2.2.2单边积分型A/D转换器 2. 2.3象素级集成(Pixel Level) 目前用于象素级的A/D转换器主要有Fowler[4]提出的过采样Sigma-Delta结构A/D转换器和Yang提出的MultiCChannelCBitCSerial(MCBS)结构A/D转换器. 2.3.1 精简型过采样Sigma Delta结构A/D转换器 输入信号过采样后经过积分器积分,然后通过量化器反馈回输入端,同时输出量化后的数字信号,数字信号经过梳状滤波器降频到Nyquist频率。 Fowler利用Sigma-Delta A/D转换器得思想对传统Sigma-Delta A/D转换器进行改进,精简了电路,提出的CMOS象素级集成的精简型Sigma-Delta A/D转换器电路。

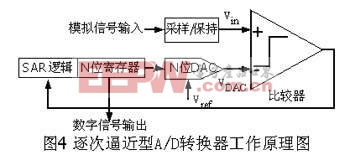

逐次逼近型A/D转换器可以提供8位到18位,速度最快在5Msps左右的模数转换。它使用了一个比较器,一个采样保持电路,一个N位的DAC,一个N位的移位寄存器和一个SAR逻辑。这种结构利用数据不断通过环路逐次逼近的方法来达到所需要的精度。想要达到N位的精度就需要循环比较N个周期。这种循环利用结构的缺点是A/D转换器的采样速度较慢。优点是芯片面积小。这种类型A/D转换器的另一特点是电路的功耗随采样率成比例增加,而不像全并行和流水线类型A/D转换器的对应采样率有固定功耗。逐次比较型A/D转换器在R. Panicacci等人的图像传感器芯片中成功的列级集成,并且得到了很好的应用效果。

单边积分型A/D转换器可以提供高精度的模数转换,并且具有很好的噪声抑制。单边A/D转换器的工作原理是一个未知输入电路电压VIN通过RC电路进行积分。积分结果VINT与已知参考电压VREF进行比较。已知积分后的电压VINT比输入的VIN电压和积分时间t成比例关系,即VINT/VIN和达到的积分时间成比例关系。所以可以根据TINT等于VREF所耗用的时间来确定VIN的大小。

这种结构A/D转换器的制约因素是 的精度和RC的精度。因此参考电压,电阻和电容微小的变换都会影响转换精度。设计中成功使用了单边积分型A/D转换器与芯片进列级集成。

2.2.3周期型A/D转换器

周期型A/D转换器在原理上类似流水线结构A/D转换器。它在结构上相当于流水线 A/D转换器中的一阶,通过多周期调用达到所需要的精度。工作原理是输入信号在读入控制信号上升时被读入电路,然后在A/D转换器电路中被采样,结果存入寄存器输出,再通过一个DAC后和原信号相减。剩余信号通过采样保持放大器,放大到原来大小,在反馈控制信号上升时进行下一次采样。这种周期性重复使用的结构降低了功耗,提供了中低速的模拟信号到数字信号的转换。1998年S. Decker[8]教授在ISSCC会议上发表了采用该种结构A/D转换器,采用0.8 工艺,5v电压,用于256×256象素的图像传感器芯片。

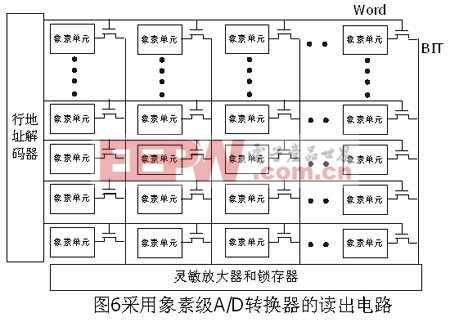

象素级集成的特点是采用每个光电检测器(Photodetector)或者几个光电检测器共用一个低速A/D转换器,大量低速A/D转换器并行工作达到一个高速A/D转换器的效果。象素级A/D转换器使得图像传感器中心与周边的通讯由模拟信号改变为数字信号,减少了原来模拟信号传输过程中信号的损失。象素级A/D转换器和象素传感器集成带来了图像传感器结构上的重复性,从而使图像传感器内部具有很多重复单元,因而具有可扩缩性。虽然象素级A/D转换器有着诸多优点,但是象素级A/D转换器由于集成在象素单元内,A/D转换器面积上受到填充率(fill factor)的限制,而且A/D转换器数目和传感器象素单元个数处在同一数量级上,所以象素级A/D转换器对功耗和面积的要求非常的苛刻,故而传统A/D转换器结构很难作为象素级A/D转换器与图像传感器集成。

图6就是一个使用了象素级A/D转换器的读出电路原理图,它由N×M的象素单元阵列,行解码器,高精度放大器和列地址解码/输出复选器组成。其中一个A/D转换器和多个光电检测器一起构成一个象素单元。

过采样Sigma-Delta A/D转换器的特点是模拟部分比例少,精度要求低,(减小了Vdd波动,器件匹配,KT/C噪声对电路性能的影响),数字部分比例大,比较适宜用标准CMOS工艺实现。一阶过采样Sigma-Delta的结构简单、速度低、精度高,恰好满足了图像传感器对象素级A/D转换器的要求。一阶过采样Sigma-Delta结构A/D转换器原理如图7所示。 信息来源:http://tede.cn  信息来自:输配电设备网

信息来自:输配电设备网

它的一个单元采用了四个光电检测器和一个象素级A/D转换器,并且通过17只管子来实现。工作时,由于感光后光电二极管产生了光电荷,光电荷储存在光电二极管节电容中产生了节点电压,转换器通过被复选器选中一个光电二极管,被选光电二极管的节电压通过受时钟控制比较器被量化。

该设计中比较器工作于亚阈值区以减少功耗和噪声,增加增益,并且减小D/A转换器中的漏电流。偏置电流也被设置成能够够完成所需要采样率的足够小值,。这一位的D/A转换器是通过一个模拟信号移位寄存器来实现。

于数字部分比较复杂,占用的面积大,Fowler只把Sigma-Delta A/D转换器的模拟部分集成与图像传感器芯片中,而把数字部分放在片外。这种做法缩小了芯片面积,但是过采样会导致输出数据量巨大,由于数字部分设置在片外,这样对于大尺寸或者高速CMOS图像传感器芯片,需要很高的I/O带宽,所以限制了它的应用范围。

2.3.2 MCBS结构A/D转换器

传统的位并行(bit parallel)和位串行(bit serial)A/D转换技术在面积,功耗上的限制无法做为象素级集成的A/D转换器使用。1998年Stanford 大学的学者David Yang提出了第一种Nyquist率的MCBS(multi-channel-bit serial) 结构的象素级A/D转换器,它的采样频率只有信号频率的2倍,所以不会有信号输出数据量过大的问题。它由象素单元电路和芯片级电路组成,每一个象素单元采用了一个比较器和一个锁存器构成。而所有象素单元共用一个有限状态机电路和一个M位的DAC电路。 信息请登陆:输配电设备网

- 德州仪器高性能模拟运放产品系列介绍集锦(11-13)

- CMOS求和比较器在PWM开关电源控制中的应用(11-27)

- 如何将CMOS LDO应用于便携式产品中(01-15)

- 2.5 Gb/s 0.35μmCMOS光接收机前置放大器设计(01-22)

- 用于下一代移动电话的电源管理划分(08-28)

- 不同电源供电的器件间的桥接(04-27)