优化位定时提高CAN 网络性能的研究

随着 CAN 总线的应用越来越广泛,对如何提高CAN 总线网络的性能就显得尤为重要。 CAN 总线允许用户自行设计采样点位置和采样次数来优化应用网络的性能。而振荡器容差 和总线长度是互相冲突的,只有通过优化位定时参数才能使二者兼备。本文深入分析了CAN 总线的位定时参数、参考振荡器容差和信号传播延迟之间的关系,提出了一种切实可行的优 化方法,并采用独立CAN 控制器SJA1000 构建实验平台,经验证该方法是有效的。

1 位定时控制方法分析

1.1 位时间

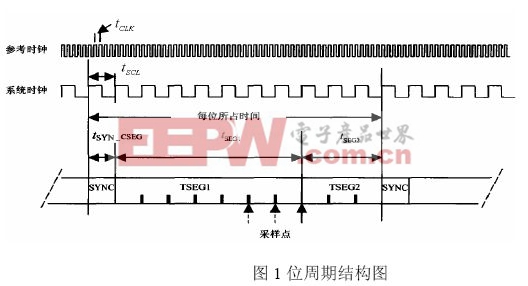

位时间即位周期是指一位的持续时间。额定位周期tBit由同步段SYNC_SEG、相位缓 冲段TSEG 1 和TSEG2这3个时间段组成。

额定位周期中这些段都由整数个基本时间单位来表示,称为时间份额(TQ),而时间份 额由振荡器时钟周期CLK t 和波特率预分频值BRP 取得。

简言之,位定时的作用可归纳为:1)确定位时间,以便确定波特率,进而确定总线的 网络速度;或在给定总线的网络速度的情况下确定位时间;2)确定1 位的各个组成部分的 时间长度;3)确定重同步跳转宽度以用于重同步。

1.2 传输延迟

CAN 总线中的节点通过非破坏性仲裁访问网络,总线上的所有节点都要同步于最先开 始发送的节点,但是节点之间竞争优先权时会产生传输延迟,使节点的同步达不到理想值。 如果传输延迟时间过长,将导致无效的访问仲裁。同时,CAN 总线中的各种延迟在给定位 速率下还会限制最大的网络总线长度。

如图 2 所示,节点A 和节点B 都是发送节点,因此总线要对两个节点进行仲裁。节点 A 比节点B 提前发送不到1 个位时间,当节点B 收到延迟后的跳变沿时,节点B 要同步于 节点A,对位时间进行移相。移相后节点B 发送的标识符有较高优先级,因此赢得总线的 使用权,同时节点B 发送的显性位经过延迟后到达节点A。

因为存在振荡器容差,节点A 的采样点在相位缓冲段的位置是不能确定的,所以节点B 发送的位流必须在节点A 的相位缓冲段1 开始之前到达,因此传播时间段的长度将受到这 个条件的限制。

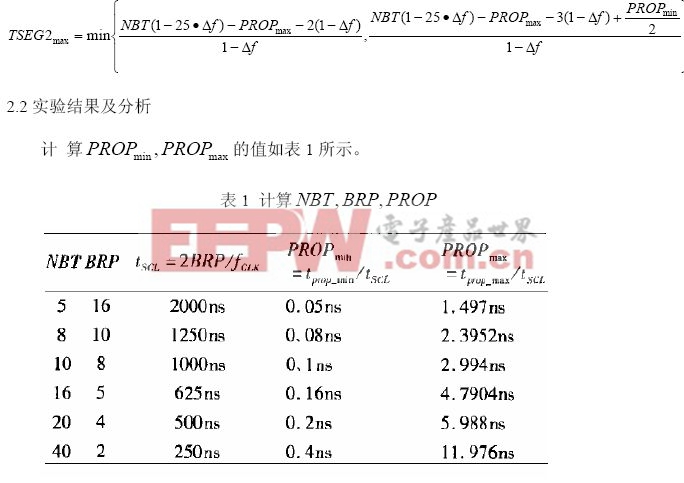

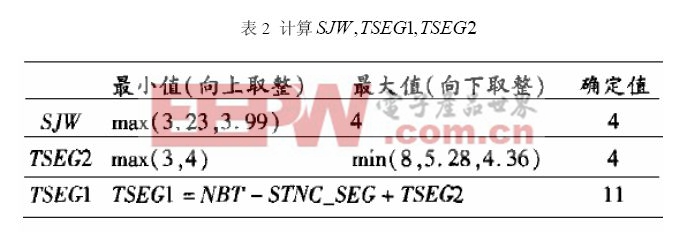

2 位定时参数的计算

2.1 实验方法及软件设计

CAN 系统的最小要求是有两个节点,本实验系统由4 台插有CAN 适配器的PC 机构成, 4 台PC 机分别定义为节点1、节点2、节点3、节点4。该适配器以独立CAN 控制器SJA1000 为核心,SJA1000 是由PHILIPS 公司生产,支持PeliCAN 模式。

独立CAN 控制器SJA1000 中,总线定时寄存器0(BTR0) 用来定义波特率预设值BRP 和同步跳转宽度SJW 的值,总 线定时器1 用来定义每个位周期的长度、采样点的位置,以 及在每个采样点的采样数目。

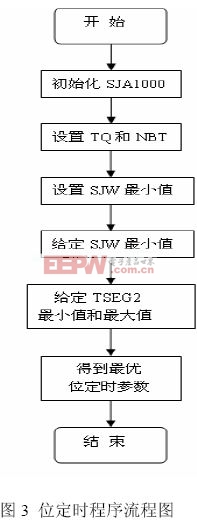

本系统采用低波特率通信,因此选择3 采样点模式,基 于以上讨论及SJA1000 的特点,可以设计出CAN 总线位定 时计算的软件,其流程图如图3 所示。

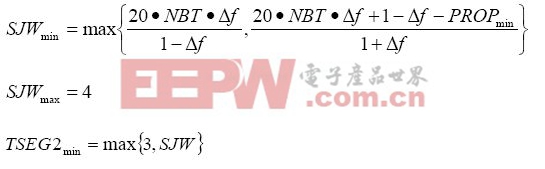

选 择 3 采样点模式时位定时的计算公式如下:

当表 2 中计算出的TSEG2的最小值和最大值出现冲突时,需要减少期望的最大传播延迟和 使用容差更小的振荡器来重新计算位定时参数。

3 结论

优化位定时时间能大大提高 CAN 总线网络的性能,本文提出的方法能有效的得到最优 的位定时参数,实验证明该方法是可行和有效的。本文作者创新点:设计系统采用低波特率 通信,针对传输延迟和振荡器容差编写出最优位定时参数计算程序,该方法能应用到CAN 总线节点开发中。

- 基于CAN总线的RS-232串口设备远程通信(01-18)

- 现场总线CANbus与RS-485之间透明转换的实现(01-26)

- 支持CAN总线的电动车辅助逆变电源的设计(02-23)

- 单片机和MCP2510的CAN息线通信模块设计(05-03)

- CAN总线/RS232接口的设计(10-12)

- 机车空调逆变电源控制系统及其实现(06-21)