基于LED的视频显示板设计

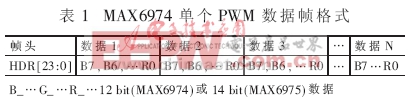

除传递每个端口的PWM信息外,帧头CMD位为010101、101010和111111的3个数据帧,通过MAX6974 LVDS接口传送CALDAC、全局亮度PDM和配置信息,如表2。每个帧头包含24 bit,第一字节为同步模板11101000,随后是6 bit CMD和10 bit计数器值(CNTR)。每个端口PWM数据帧的CMD位是000000。

除PWM信息外,数据帧也利用基于PC的GUI通过DVI接口发送。数据帧类型由FPGA内部的相应电路识别。在一个控制视频帧内,0至1行的每个像素都包含24 bit帧头配置信息(HDR);第32行和33行包含全局亮度PDM的帧头信息,第64行和65行包含CALDAC的帧头信息。本参考设计中,每组2行帧头之后的30行数据对应于LED显示模块PCB的30行信息。每个特定的LVDS列提供每行64像素的信息,用于传输每块LED显示模块PCB上64片MAX6974 LED驱动器的信息。每片MAX6974器件的每个像素包括24 bit控制信息,视频帧控制中不使用95行以上的数据。

1.5 视频显示板控制GUI

GUI如图3,用于配置参考设计中所有MAX6974的全局亮度PDM和CALDAC寄存器。GUI包括一个全局设置选项,用于调节视频显示板上所有芯片的相关参数,还包含一个器件制表符,用于调节每个芯片的参数。所有寄存器和MAX6974 LED驱动器的设置可以存储到一个文件,当视频显示板运行时下载数据。提供一个初始化设置文件,其中包括典型的寄存器参数的初始设置,大大简化了视频显示板的初始化过程。

GUI作为一个独立的操作窗口出现在Windows操作系统。一旦使能GUI上的Write按钮,它将创建一个视频控制帧并将其发送到视频显示板。视频控制帧只能按照60 Hz的视频刷新率显示。视频控制帧也会占据视频显示板的整个屏幕;而FPGA会检测控制帧头行并将相应的信息发送到MAX6974寄存器。因此,视频控制帧的内容不会显示在视频显示板上。虽然视频帧刷新时也会传递控制信息,但人眼不会注意到这些更新。

2 方案实施

DVI接收板包括TFP401 DVI接收器和AT24C02 EEPROM,另外还有几个旁路电容。TFP401 DVI接收器实现串并转换和TMDS解码,并保证在半像素时钟速率下同时得到RGB位的奇、偶像素。因为DVI决定屏幕的最小分辨率是VGA,参考设计消除了每个邻近像素,支持隔行扫描。半像素时钟对于FPGA非常便利,允许其挑选所需要的像素。在Windows操作系统识别显示器之前,通过DDC按照I2C协议检测显示器。然后,该显示器响应其EDID,包含制造商信息和操作信息。同样,AT24C02 EEPROM用于储存LED视频显示板的EDID信息。制造商ID必须从视频电子标准协会(VESA)获取,本参考设计中,借用DVI LCD显示器的EDID,储存在AT24C02 EEPROM中。当所有的3个地址引脚接地时,AT24C02 EEPROM的I2C地址是0x0A,这是操作系统将要搜索的地址。

FPGA板主要包括2个SRAM和1片Altera?RFPGA器件。FPGA内部具有LVDS接口和存储器读取功能。该参考设计中,FPGA主要用于DVI数字视频信息的输出分配。FPGA的另一重要作用是识别数据帧配置、全局亮度PDM和CALDAC信息。当识别到视频控制帧时,这些数据帧中除了独立的PWM信息外,都被接收下来并直接发送到相应的MAX6974寄存器。

图4给出了FPGA的内部功能电路,一帧像素的数据位存储在SRAM缓存内。FPGA内部的行缓存器用于连接TFP401A DVI接收机和LVDS通道。两行缓存器,一行用于接收TFP401A接收的数据位,连接SRAM的另一行缓存器用于接收TFP401A DVI接收机的数据。同样,两行缓存器用于每个LVDS通道。FPGA提供完整的逻辑电路使DVI和LVDS数据吞吐率保持一致,并提供所要求的SRAM数据、地址以及控制信号的时序。因为SRAM为单端口,同时进行读、写操作时需要在FPGA内部配置存储器访问。

每片MAX6974驱动8个RGB LED,每个显示模块包含64个MAX6974 LED驱动器,按照8行、8列分布,另外还有8行、64列的512个RGB LED。所有LED安装在PCB的一侧,LED中心距离为8 mm(上、下、左、右间距),显示模块电路板尺寸为512 mm×64 mm。所有MAX6974器件都安装在PCB的另一侧。在安装MAX6974器件的一侧,铺设电源和地线,包括1×6接头,共需2组1×6接头:一个用于左上角的LVDS输入接口,另一个用于左下角的LVDS输出接口。显示模块电路板可以嵌在视频显示板框架上,所有互联板都安装在框架内。邻近LED显示模块PCB之间的LVDS接口不需要额外引线。

3 功耗

3.3 V VCC供电时,每片MAX6974的工作电流为28 mA(CALDAC关闭)或54 mA(CALDAC使能)。一个LED显示模块PCB上包含64个LED驱动器,工作电流为1.8 A或3.5 A。采用5 V VLED供电时,MAX6974每个端口提供的最大LED电流为30 mA。512个RGB LED显示模块的最大电流为46 A,需要多个3.3 V和5 V电源为整个视频显示板供电。

- 为手持设备的被动式OLED显示器供电(11-25)

- 选择用于无线产品的LED驱动 (11-25)

- 利用EL7516作为高效、高电流的白光LED驱动器 (11-29)

- 背光驱动电路的选择策略和应用介绍(01-09)

- 改善 PWM 电源控制器低负载运行的缓冲放大器和 LED(01-16)

- 手机白光LED驱动电路解决方案分析(01-10)