低成本高精度、高系统分辨率的多路复合系统

一般而言,手持式仪表、数据记录器、车载和监控系统都要求一种低成本高精度、高系统分辨率的多路复合系统。可以将这些要求都集成到一个电路中吗?能够处理这些多样性需求的系统,要求一个多路复用器、增益单元和一个模数转换器(ADC)。

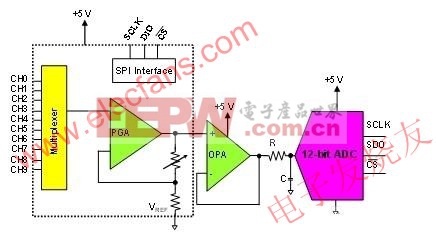

解决这个问题的一种可行方案是一个10通道、可编程放大器(PGA),它与一个中速12位SAR ADC(请参见图1)配合工作。该单电源、10通道PGA具有一个轨至轨的输入/输出,增益调节范围为1V/V到200V/V。PGA的12nV√Hz @ 10kHz低噪声性能适合于12位系统。这两个器件之间的模拟接口包括一个缓冲结构的运算放大器(OPA)以及一个R/C电路。12位ADC是一个带固有采样和保持的电容型SAR ADC。该转换器要求R/C电路,其可简化ADC输入结构的充电动作。

图1:这种系统使用一个多路复用PGA和驱动12位转换器的运算放大器。

计算得到的PGA噪声值(参考输出(RTO))等于10kHz下PGA噪声密度(12nV/√Hz)乘以PGA闭环带宽的平方根乘以√(p/2)。√(p/2)的倍数说明了PGA带宽以外频率区域的噪声。之后,所得值再乘以PGA的增益。方程式1使用了16V/V的PGA增益:

PGArms-noise=12nV/√Hz*√(1.6MHz*√/2)*16V/V=0.304mV(rms) 方程式1

转换器产生的ADC噪声为431mV(rms),大大低于该5伏系统的1LSB或1.22mV。缓冲放大器的噪声为39mV(rms),带给系统的噪声极少甚至为零。

PGA、OPA和ADC的组合噪声为529 mV(rms),仍然低于12位转换器的1LSB。该值使用一个方和根方程式(即方程式2) 计算得出:

Noise(RTO) = √(PGArms-noise2 +OPArms-noise2 + ADCrms-noise2) 方程式2

PGA为16 V/V增益时该系统的等效12位精度(Equiv12-bit)为0.432LSBs(请参见方程式3)。

Equiv12-bit = (NoiseRTO * 2N)/FSR, {where N = 12 and FSR = 5 V/V} 方程式3

如果我们在1-200 V/V的PGA增益范围来观察该系统,我们便会发现PGA噪声为电路的主要噪声。一旦PGA增益超出~125 V/V,该系统便不再符合12位精度标准。然而,这种情况能够通过缩小系统参考输入LSB的电压大小来改善(请参见图2)。获得更小LSB的折中方法是降低系统的有效转换位数(ENOB)。

图2:系统精度高于0.01%,且PGA增益为1-125V/V。

图1 所示系统可在要求12位精度时提供足够的PGA增益范围,也可在要求高系统分辨率时提供同样足够的增益范围。

- 一种新型高精度CMOS带隙基准源的设计(09-12)

- 高精度自动校时钟在中波转播台中的应用(10-25)

- 基于DPWM的高速高精度积分型模数转换器(11-05)

- 高速高精度流水线模数转换器的设计(12-09)

- 高精度的温度传感电路设计(03-09)

- 基于TMS320F2808的高精度UPS电源锁相技术(11-16)