高速PCB设计下的EMI规则探讨

时间:01-24

来源:互联网

点击:

随着,信号上升沿时间的减小,信号频率的提高,电子产品的EMI问题,也来越受到电子工程师的光注。高速PCB设计的成功,对EMI的贡献越来越受到重视,几乎60%的EMI问题可以通过高速PCB来控制解决。

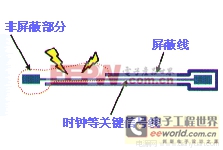

规则一:高速信号走线屏蔽规则

如上图所示:

在高速的PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都是会造成EMI的泄漏。

建议屏蔽线,每1000mil,打孔接地。

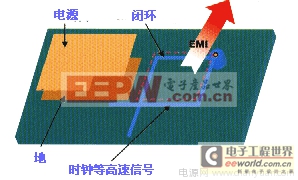

规则二:高速信号的走线闭环规则

由于PCB板的密度越来越高,很多PCB LAYOUT工程师在走线的过程中,很容易出现这种失误,如下图所示:

时钟信号等高速信号网络,在多层的PCB走线的时候产生了闭环的结果,这样的闭环结果将产生环形天线,增加EMI的辐射强度。

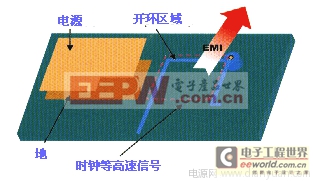

规则三:高速信号的走线开环规则

规则二提到高速信号的闭环会造成EMI辐射,同样的开环同样会造成EMI辐射,如下图所示:

时钟信号等高速信号网络,在多层的PCB走线的时候产生了开环的结果,这样的开环结果将产生线形天线,增加EMI的辐射强度。在设计中我们也要避免。

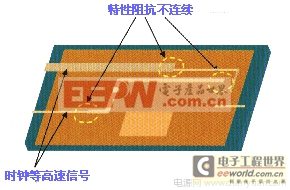

规则四:高速信号的特性阻抗连续规则

高速信号,在层与层之间切换的时候必须保证特性阻抗的连续,否则会增加EMI的辐射,如下图:

也就是:同层的布线的宽度必须连续,不同层的走线阻抗必须连续。

- 电源管理总线的结构与优势(11-19)

- 如何设计一个合适的系统电源(上)(11-20)

- 新型灌封式6A至12A DC-DC μModule稳压器系列(11-19)

- 如何设计一个合适的系统电源(下)(11-20)

- PCB电源供电系统的分析与设计(11-21)

- LVDS技术原理和设计简介(01-26)