组合逻辑电路的设计

组合逻辑电路的设计与分析过程相反,其步骤大致如下:

(1)根据对电路逻辑功能的要求,列出真值表;

(2)由真值表写出逻辑表达式;

(3)简化和变换逻辑表达式,从而画出逻辑图。

组合逻辑电路的设计,通常以电路简单,所用器件最少为目标。在前面所介绍的用代数法和卡诺图法来化简逻辑函数,就是为了获得最简的形式,以便能用最少的门电路来组成逻辑电路。但是,由于在设计中普遍采用中、小规模集成电路(一片包括数个门至数十个门)产品,因此应根据具体情况,尽可能减少所用的器件数目和种类,这样可以使组装好的电路结构紧凑,达到工作可靠而且经济的目的。

下面举例说明设计组合逻辑电路的方法和步骤。

例1:试用2输入与非门和反相器设计一个3输入(I0、I1、I2)

、3输出(L0、L1、L2)的信号排队电路 。它的功能是:当输入I0为1时,无论I1和I2为1还是0,输出L0为1,L1和L2为1;当I0为0且I1为1,无论I2为1还是0,输出L1为1,其余两个输出为0;当I2为1且另外两个均为0时,输出 L2为1,其余两个输出为0。如I0、I1

、I2均为0,则L0、L1、L2也均为0。

解:

(1)根据题意列出真值表如下:

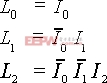

(2)根据真值表写出各输出逻辑表达式:

(3)根据要求将上式变换为与非形式:

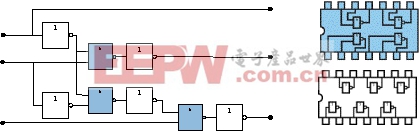

由此可画出逻辑图,如下图所示。该逻辑电路可用一片内含四个2输人端的与非门(图中蓝灰色部分)(比如74LS00)和另一片内含六个反相器(74LS04)的集成电路组成。原逻辑表达式虽然是最简形

式,但它需一片反相器和一片3输入端的与门才能实现(见下图),器件数和种类都不能节省,而且三输入端的与门器件不如二输入端的与非门常见。由此可见,最简的逻辑表达式用一定规格的集成器件实现时,其电路结构不一定是最简单和最经济的。设计逻辑电路时应以集成器件为基本单元,而不应以单个门为单元,这是工程设计与理论分析的不同之处。

例2 试设计一可逆的4位码变换器。在控制信号C=1时,它将8421码转换为格雷码;C=0时,它将格雷码转换为8421码。

解:

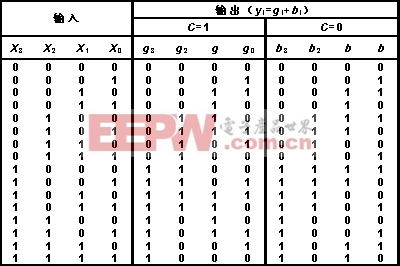

(1)列出真值表如下:

当C=l时,输入X3X2X1X0作为8421码,对应的输出g3g2g1g0为格雷码;

当C=0时,输入则作为格雷码,对应的输出b3b2b1b0为8421码。此时,X3X2X1X0作为格雷码的排列顺序体现在它与b3b2b1b0的——对应关系。

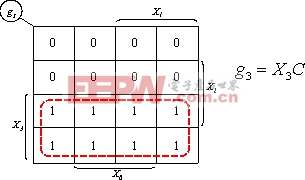

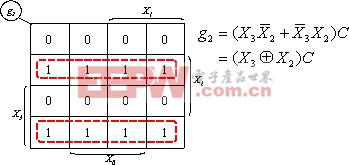

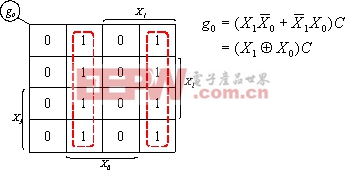

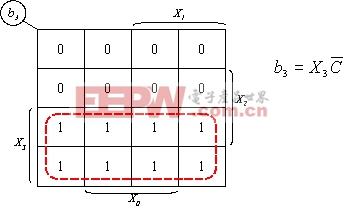

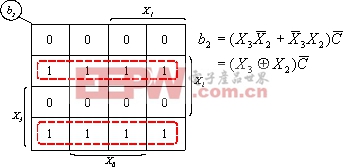

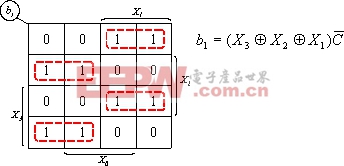

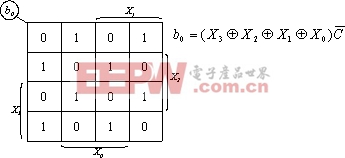

(2)分别画出C=l和C=0时各输出函数的卡诺图和对应的输出逻辑表达式如下:

C=1时有:

C=0时有:

(3)写出总的输出逻辑表达式:

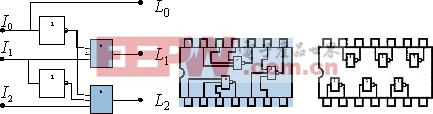

(4)画出逻辑图:

从以上逻辑表达式和逻辑图可以看出,用异或门代替与门和或门能使逻辑电路比较简单。在化简和变换逻辑表达式时,应尽可能使某些输出作为另一些输出的条件,例如,利用Y2作为Y1的一个输入,Yl又作为Y0的一个输入,这样可以使电路更简单。在化简时,若注意综合考虑,使式中的相同项尽可能多,则可以使电路得到简化。此外,我们还将与或换成与非形式,从而减少了门电路的种类 。该逻辑电路可由两片各含四个2输入端的与非门(740)和一片内含四个异或门(7486)的集成电路组成。

模拟电路 模拟芯片 德州仪器 放大器 ADI 模拟电子 相关文章:

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- PIC16C5X单片机睡眠状态的键唤醒方法(11-16)

- 用简化方法对高可用性系统中的电源进行数字化管理(10-02)

- 利用GM6801实现智能快速充电器设计(11-20)