降低电感磁芯损耗的解决方案

时间:10-25

来源:互联网

点击:

您是否有过为降压稳压器充电、进行满功率测试,随后在进行电感指端温度测试时留下了永久(烫伤)印记的经历呢?或许过高的磁芯损耗和交流绕组损耗就是罪魁祸首。在 100-kHz 开关频率下,一般不会出现任何问题,这是因为磁芯损耗约占总电感损耗的 5% 到 10%。因此,相应的温升才是问题所在。一般而言,选择电感时,只需计算出最大负载电流,通过容许 20% 纹波电流来建立电感。由于磁芯损耗微不足道,因此会出现类似于产品说明书中所示的温升。然而,随着开关频率上升至 500 kHz 以上,磁芯损耗和绕组交流损耗可以极大地减少电感中的容许直流电流。使用 20% 纹波电流来计算电感,可带来相同的磁芯材料通量激增,其与频率无关。磁芯损耗方程式的一般形式为:

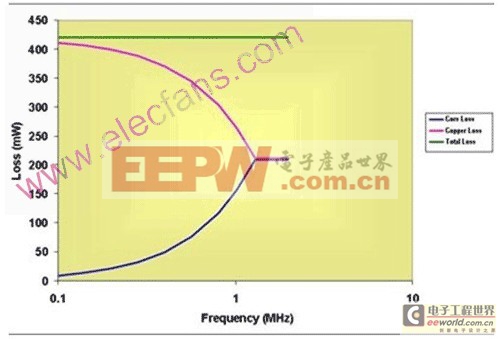

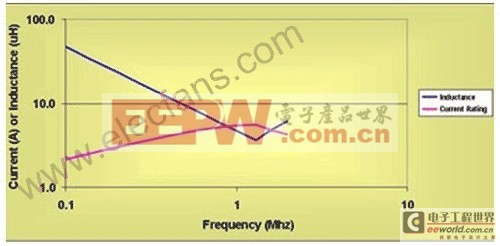

Pcore = K × F1.3。因此,如果频率 (F) 从 100 kHz 升至 500 kHz,则磁芯损耗便为原来的 8 倍。图 1 显示了这种上升情况,还描述了随磁芯损耗上升而下降的容许铜线损耗。100 KHz时,大多数损耗存在于铜线中,同时利用全直流额定电流是可能的。更高频率时,磁芯损耗变大。由于总容许损耗由磁芯损耗与铜线损耗之和决定,因此铜线损耗必须在磁芯损耗上升时降低。这种情况一直持续到各损耗均相等。最佳情况是,在高频率下损耗稳定保持相等,并允许从磁结构获得最大输出电流。

总之,增加开关频率会缩小磁芯尺寸的看法是正确的,但仅限于磁芯损耗和交流 绕组损耗等于铜线损耗的点上。过了这个点,磁芯尺寸实际上会增加。另外,设计人员需要注意的是,在有许多高开关频率产品可供选择的今天,一些相应的应用手册中并没有清楚地注明过高磁芯损耗存在的一些潜在问题。

- 电感三点式振荡电路(01-24)

- 为DC/DC转换器选择正确的电感器与电容器(01-02)

- 开关电源电感器的选用(06-18)

- 利用电感型转换器设计提高LED转换效率(10-05)

- 并联混合滤波器中连接电感的仿真研究(10-30)

- 功率电感对电源的改善(10-21)