PCI9656介绍及其应用实例

PCI9656是PLX公司推出的一种64位、66MHz的PCI接口电路。具有灵活的连接性能和高性能的I/O加速器特性,用于PCI、Compact PCI和嵌入式主机设计。文中主要介绍PCI9656的功能、特点及应用,给出具体应用实例,同时指出应用中需注意的问题。

引言

PCI总线协议比较复杂,因此它的接口电路实现起来也比较困难。它不但有严格的同步时序要求,而且这了实现即插用和自动配置,PCI接口还要有许多的配置寄存器。对于一般的设计者来说,为了缩短开发周期,没有必要设计所有的接口逻辑,只要利用通用PCI接口电路就能很好的进行开发设计,从而大大减轻了工作难度。

目前,业界基于32位PCI总线使用较多的接口芯片是AMCC公司的S59xx系列和PLX公司的PLX系列。而现有普通计算机公司均已采用32位架构,系统的内存寻址能力已达到4GB,因此,32位PCI总线已经不能满足日益庞大的数据处理需要。鉴于英特尔公司推出的Itanium处理器直接从32位跃升到64位,因此,开发基于64位PCI总线的接口设备显得尤为重要。下面介绍一款PLX公司的基于64位PCI总线的PCI9656型接口电路。

1 PCI9656概述

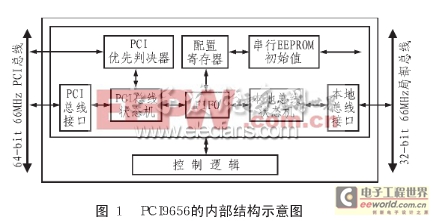

PCI9656是PLX公司为扩展适配板卡推出的能提供混合高性能PCI总线目标模式的接口电路,该接口电路可提供用于适配卡的小型高性能64位PCI总线目标接口。PCI9656的内部结构框图如图1所示。它的主要特点如下:

●符合PCI V 2.2协议,支持64位、66MHz时钟PCI总线,特别适用于PCI总线外设产品开发。

●采用PLX数据流水线架构(Data Pipe Architecture)技术,配有DMA引擎、可编程直接主控或者直接从属数据传输模式以及PCI信息传输功能。

●具有PCI优先判决器,可以支持7个外部主控器。

●可以由2个局部总线中断信号LINTi和LINTo生成一个PCI中断信号INTA。

●局部时钟与PCI时钟异步工作,允许局部总线独立于PCI时钟工作。

●支持多路复用和非多路复用的8位、16位和32位66MHz时钟局部总线。

●可直接生成所有的控制、地址和数据信号以驱动PCI总线,不需要额外驱动电路。

●可通过消息管理系统I/O,并提供2种方式选择,一是通过邮箱寄存器和门铃寄存器,二是通过所提供的I2O接口。

●寄存器PCI9054寄存器兼容,可容易地进行基于32位PCI总线与基于64位PCI总线的软件移植。

2 PCI9656的功能

PCI9656可用来为非PCI设备和PCI总线提供数据通道。下面介绍具体操作功能。

2.1 初始化

在上电时,PCI总线的RST信号将PCI9656的内部寄存器设置为缺省值,同时,PCI9656输出局部复位信号(LRESET)并检查EEPROM是否存在。如果系统上装有EEPROM且该EEPROM的第一个16字节非空,则PCI9656将根据EEPROM内容设置内部寄存器,否则设为缺省值。

2.2 复位

PCI总线的RST信号有效时,整个PCI9656将复位,同时,输出LRESET局部复位信号。另外PCI总线上的主控设备也可以通过设置寄存器中的软件复位比特来对PCI9656进行复位,但是主控设备只能访问配置寄存器而不能访问局部总线。所以,PCI9656公一直保持这种复位状态直到PCI主控设备清除软件复位比特。

2.3 串行存储器接口(EEPROM)

复位后,PCI9656将开始读串行EEPROM,START为0表示EEPROM存在。此时若该EEPROM的第一个字(16bit)既不为“全1”(EEPROM为空)也不为“全0”(EEPROM不存在),PCI9656将用它进行配置。如START为1,表示EEPROM不存在或EEPROM为空,PCI9656采用缺省值配置。

PCI9656总线上的主机可以对串行EEPROM进行读写,寄存器位[31,27-24]控制着PCI9656对EEPROM位的读写。将重载配置寄存器位CNTRL[28]置1可以用串行EEPROM重新配置PCI9656。EEPROM的时钟可由PCI总线时钟分频获得。

PCI9656 相关文章:

- PCI9656型64位PCI总线接口电路及其应用(01-18)

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- PIC16C5X单片机睡眠状态的键唤醒方法(11-16)

- 用简化方法对高可用性系统中的电源进行数字化管理(10-02)