如何用Allegro对s3c2410的BGA封装布线

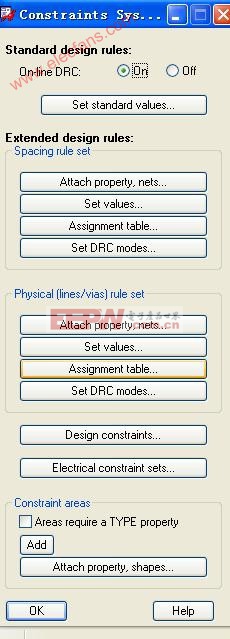

由于s3c2410或者2440是采用的BGA封装,看了网上专门有BGA封装的电子资料,是介绍规则的,但是我感觉做起来非常麻烦,所以就觉得是否可以采用最直接的办法使用allegro的扇出功能呢?首先是设置通孔,这个在约束条件管理器中设置

点击物理规则(physical rule set)设置中的Set values

一定注意这个地方的设置如果你想采用的过孔没有出现在左边的方框内,请查看是否正确设置了user preference设置中的Design_paths中的psmpath和padpath,我是把自己放置通孔的路径增加进去了。

这种方式是最直接修改过孔的办法,另一种是在过孔以后使用tools->padstack->replace功能来替换,那个比较麻烦。还是设置约束规则比较好。

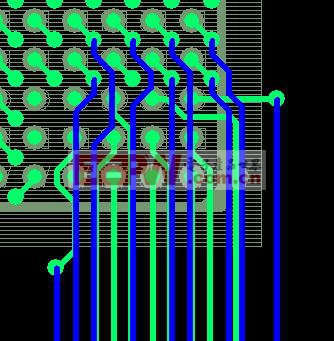

设置好了通孔我们就用扇出功能,在Route点击Fanout By Pick,这时可以右键鼠标选择setup对扇出进行设置,然后选中s3c2410/2440,此时就会看到扇出后的效果了。

感觉很漂亮而且符合BGA布线的规则,即发射形状,不过最外边的那一排不需要扇出,所以在菜单Edit->delete,然后在过滤Find中只选择Clines和Vias,一般是把四周最外边的三排全部删除了,也可以在布线的同时修整扇出,现在开始对其进行布线了,不过根据布线的走向和密度我决定先从通孔引出到封装外部再进行群组走线,点击Route-Connect,一定要注意右边Options中的Bubble选择正确,如果是Shove preferred(推挤前面的)就会把相邻的布线给挤掉了,如果选择Hug preferred(拥抱前面的)就会在邻近的布线时出现合并现象,这也是不允许的,如果是Off就不会自动避开相近的布线,而Hug only就只是靠近或者拥抱相邻的布线不会出现合并,所以在这里选择Hug preferred。这是最重要的因为选择不正确就会布一条挤掉或者合并了前一条,我就是在Options选项上郁闷了半天,看来出现问题时需要的是先查找有关的工具手册看看选项中是否可以有设置项,这里就是有朋友提醒我才看到的,因为要先引出而不是连接到目标元件上,所以需要去掉clip dangling clines(剪辑悬挂的走线)和Replace etch(替换走线)这二项,保证在布线的过程中不会使走线重合或者太近。另外,因为是使用的过孔,所以可以在Options中设置想走线的层,我的是第三层的信号层,所以选择了Signal1,这个名称是我在交叉层设置中命名的。设置完毕后我的Options如下图:

下面就开始先引出BGA的走线到封装外面,以保证避开相互靠近并且可以达到群组布线目的。

我同时为顶层和第三层信号层引出了连线,然后布线时使用群组功能同时布一个层上的多条线,快到目标元件时就再次点击Done,不要直接向目标引脚引过去,因为目标引脚是贴片式的封装都在最顶层,所以对于第三层或者内层的走线需要再次过孔到顶层,为了尽量保持信号的完整性和让元件的目标引脚端的走线保持垂直,我采取从目标引脚走线向群组靠近的方法,走出的线即垂直而且好看一些。

- 在allegro中更换元件封装的方法(04-16)

- Allegro,PADS和Protel三者铺铜的比较(07-30)

- pcb layout学习中用Allegro几个误区(06-27)

- 学习allegro从了解如何建焊盘开始(06-27)

- Allegro自动及交互绕线介绍(01-02)

- 基于S3C2410和MBF200的指纹采集系统设计(01-17)