高速数字隔离型串行ADC及应用

本文研究设计了一种基于高速隔离芯片的高速串行隔离型ADC。该数字隔离型ADC频带宽,延时小,稳定性高并且电路结构简单。利用FPGA作为控制器,很好地实现了模数转换和隔离传输。

2.隔离模块基本工作原理

2.1 工程背景介绍

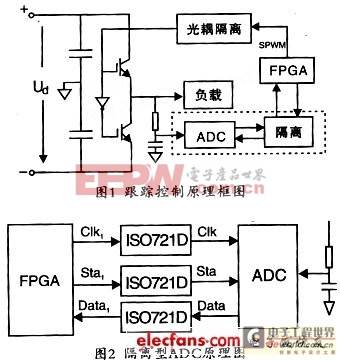

如图(1)所示为基于RC检测的跟踪控制原理框图。FPGA通过高速隔离芯片控制高速串行ADC,将电容电压实时地转换成数字量,通过隔离芯片把数字量读回到FPAG。通过这个高速隔离型ADC,即图(1)中虚线框中的部分,实时采样跟踪电压波形,根据特定的跟踪控制算法产生相应的SPWM控制信号驱动半桥主电路。假设逆变单元的开关频率为10KHz,最小占空比为10%,按照香农定理ADC采样频率至少为200KHz,在工程应用中一般留有7~10倍余量,所以高速ADC的采样频率应该在1MHz左右。MAX1072为10位单极型串行ADC,可以实现1.8MHz采样频率。可见MAX1072在采样频率和输出精度方面均满足跟踪控制的要求。同时,采用串行ADC控制引脚少,占用控制器I/O端口少,所需隔离芯片少,电路结构简单可靠性高。隔离芯片采用ISO721D,其传输带宽可达150MHz。

2.2 高速数字隔离型ADC实现原理

本论文主要研究高速隔离型ADC的实现方案,即图(1)中虚线框内的部分。此部分原理示意图如图(2)所示。图中由FPGA产生两路输出信号分别为Clk1和Sta1。Clk1经过隔离芯片输出信号Clk作为串行ADCMax1072的时钟信号其频率为24MHz。Sta1经过隔离芯片输出信号Sta作为ADC的启动控制信号其频率为1.5MHz。ADC的转换结果为Data信号,经隔离芯片输出Data1信号送回FPGA。

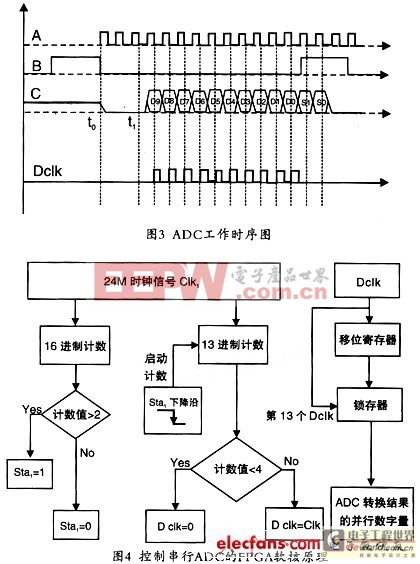

各信号相位关系如图(3)所示。其中,信号A,B,C,Dclk依次为Clk,Sta,Data和FPGA内部移位寄存器的时钟信号,实现将每一位串行数据进行存储。信号B的下降沿启动ADC进行转换,t0~t1时间段内为ADC转换时间,第四个Clk上升沿输出数字量的最高位,经4nS后稳定。依次在每个时钟信号Clk的上升沿产生数字量的下一位,在每个Dclk的上升沿将串行数据锁存在移位寄存器中。在LSB之后还有两位无效位分别为S1和S0。启动信号延时3个Clk,再进行下一次启动。

图(4)为利用FPGA实现的控制隔离型ADC的软核原理描述图。FPGA产生一路频率为24MHz的Clk,信号经过隔离芯片即为图(3)中的信号A,此信号直接输出作为Max1072的时钟信号。Clk1同时也作为启动信号的时钟信号。利用一个16进制计数器对Clk1进行计数产生信号Sta1经过隔离芯片即为图(3)中的信号B。Sta1高电平维持3个Clk1低电平维持13个Clk1。所以Sta1的工作频率为1.5MHz,占空比为12.5%。由Sta1信号的下降沿启动另外一个13进制计数器计数,产生信号经隔离芯片即为如图(3)中所示的信号Dclk。此信号作为移位寄存器的时钟信号,将10位串行数据依次移入寄存器。最后一个时钟信号启动锁存器将串行数据转换成为并行数据锁存在输出端供FPAG内部进行跟踪控制算法使用。

3.实验结果

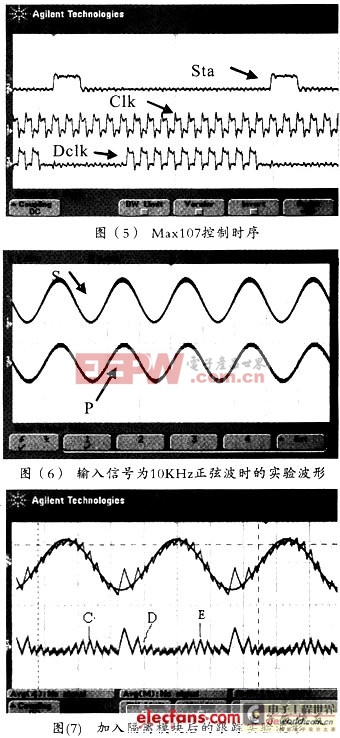

如图(5)所示,为FPGA控制Max1072的时序实验波形图参考基准电压为2.5V。图中信号Sta,Clk,Dclk分别对应图(3)中信号A,B,D。从实验结果可见Max1072的时钟频率为24MHz,启动转换信号频率为1.5MHz,与ADC时序要求完全吻合。

图(6)为隔离前后两路信号的比较情况。波形S为输入模拟信号,频率为10KHz。为调试方便外接了刷新频率为1MHz的双极型DAC。经ADC隔离采样再通过DAC将数字量转换成为模拟量即图(6)中波形P。可见数字隔离型ADC工作正常,初步验证了该方案的可行性。

图(7)为加入隔离模块后的跟踪控制原理性实验的跟踪波形。高压侧电磁干扰对控制电路的影响有很大程度地减弱。这为实现高性能的逆变单元提供了可能性。

4.结论与展望

通过实验验证了本文设计的基于高速串行模数转换器Max1072和高速隔离芯片ISO721D的数字化隔离方案的可行性。利用FPGA作为控制器初步验证了隔离模块控制时序的正确性,为跟踪型逆变单元的检测环节提供了隔离方案,有效的抑制了高压侧对控制电路的噪声窜扰。但是,由于所选DAC的性能偏低,因此没有进行更高频率信号的测试。这将在以后的工作中进一步验证和完善。

- 以数字方式管理电源的简便方法(11-30)

- 数字电位器在DC-DC变换器中的应用(11-30)

- 数字放大器对电源带来挑战(01-09)

- 热插拨和数字电源监控常见问答(01-18)

- PMBus——数字电源开放标准协议(01-18)

- 基于PIC单片机的数字式智能铅酸电池充电器的设计 (01-02)