单独集成电路的局部滤波

每块印刷电路板都需要相当多的旁路电容来抵消电源线的电感。但每块印刷电路板实际上只需要一个理想的旁路电容就可以完全解决电源分配问题。

可惜的是,没有理想的电容。每个单独的电容都有一定的串联引脚电感L,在非常高的频率上,它的阻抗将会上升,而不是下降。引脚电感是否成为问题,取决于数字转折频率F,见下式,以及必须达到的阻抗X。

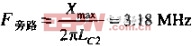

我们可以计算一个给定的旁路电容的最高有效频率:

一个大小合适的电容在频率FPSW和F旁路之间都是有效的。幸运的是,两个频率之间有一个大的间隔。

例 旁路电容的最高有效频率

根据例8.1,假设10UF电容有一个LC2=5NH的串联电感。我们要达到的XMAX为0.1欧。计算它的最大有效频率:

这个电容从159KHZ到3.18MHZ都是有效的,范围约为16:1。

一个大的旁路电容允许我们到达频率F旁路。为了保证F旁路以上的低阻抗,需要另个一个串联电厂比较低的电容。得到非常低的电感的最好方法是并联许多小的电容。可以在印刷电路板的周围散布旁路电容的并联阵列。

有3个因素将会决定电源和地之间的阻抗:

在低频,取决于电源线的电感

在中频,取决于电路板级旁路电容的阻抗

在高频,取决于分布电容阵列的阻抗

下一步是设计旁路电容阵列的过程。尽管这个过程大部分与“电源分配线的电感”中的程序类似。不同的是,“电源分配线的电感”确定了电源线的电感,但这里要设计确定局部旁路电容的串联电感。

1、我们希望系统达到频率FKNEE。计算在如此高的频率下的电厂感容限,见式()关于转折频率的定义。

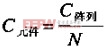

2、找出计划使用的旁路电容的串联电感LC3。一个表面安装的电容,连同非常短、宽的通孔,其典型的串联电感是1NH。一个插接旁路电容的典型串联电感值是5NH。使用这些值计算到总的目标电感所需的旁路电容数目。

3、在频率F旁路以下,电容阵列的总的阻抗必须小于XMAX,由此计算总阵列电容。

4、计算阵列中每个元件的电容。

例:电容阵列

旁路电容我们采用10UF,串联电感是5NH,我们希望得到XMAX=0.1欧。

我们需要一个由32个电容组成的阵列,每个电容为0.016UF,串联电感为5NH或更小。

- 基于新型ASSP LTC3455的硬盘MP3电源设计(06-07)

- 单片彩色LCoS显示系统的设计实现(09-09)

- 具有开关电源通路管理的下一代电源管理集成电路(08-28)

- 如何利用DCP获得更精确的性能(10-01)

- 集成电路的种类与用途(09-20)

- CMOS集成电路中ESD保护技术研究(10-17)