StellamarXilinxXC3S400AN数字ADC音频评估方案

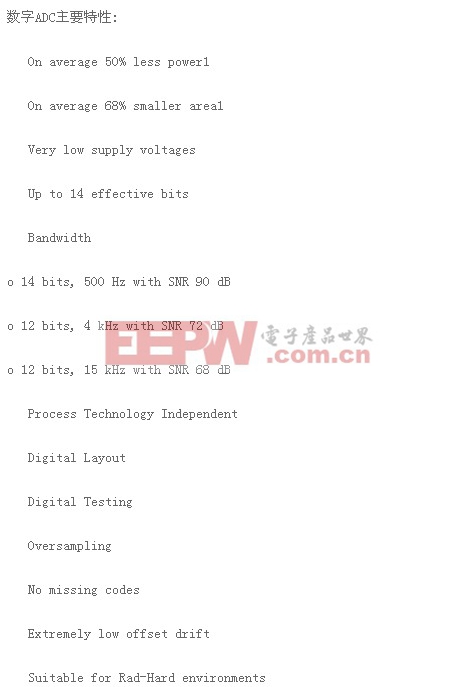

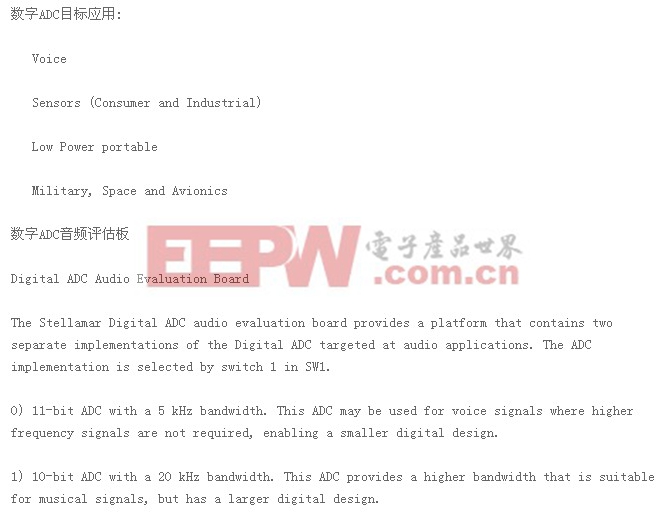

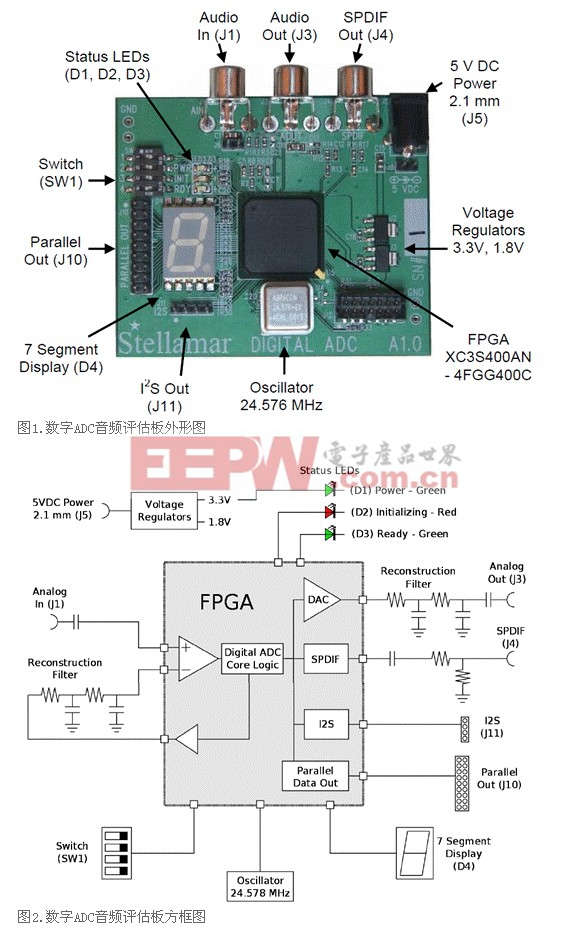

Stellamar 公司的数字ADC采用Xilinx公司的 XC3S400AN FPGA,平均功耗低50%,面积低50%,非常低的工作电压,高达14位的有效位,14位500Hz的SNR为90dB,数字典输出,数字测试,过采样,不会丢失码,极低的失调漂移,能用在苛刻的环境.目标应用在语音,消费类和工业中的传感器,低功率手提设备以及军事,空间和航空航天.本文介绍了数字ADC主要特性,数字ADC音频评估板框架图,电路图和材料清单.

The Digital ADC is a digital core which provides analog functionality with all the benefits of a digital design process: shorter design cycles, lower risk, established design and layout tools, digital test methodology, and portability across process technologies.

The design is implemented with a small number of digital gates and only an LVDS input cell, a digital output cell and a handful of passive external components.

The ADC provides up to 12 effective bits and up to 15 kHz of bandwidth making it ideal fit for both low frequency sensors and high-quality voice.

The benefits of the digital implementation include low voltage and low power process technologies where it excels in portable applications.

Alternative digital process technologies enable the Digital ADC to be used in high reliability and radiation hard environments where analog implementations are problematic.

StellamarXilinxXC3 StellamarXilinxXC S400 400 相关文章:

- 基于TPS40057的BUCK变换器(10-16)

- 常用4000系列标准数字电路的中文名称资料(04-20)

- MAX44005红外接近传感器(11-21)

- MAX44009业内功耗最低的环境光传感器(11-23)

- MAX44006,MAX44008红外和温度传感器(11-20)