CPLD与TMS320VC55x的McBSP接口设计

时间:04-18

来源:互联网

点击:

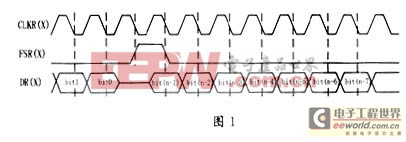

根据McBSP和CPLD的时序分析,采用VHDL语言设计了CPLD模拟McBSP并与之进行全双工通信,给出了实际的接口时序结果。

关键词:McBSP,CPLD,VHDL,DSP

在许多数字信号处理应用系统中,DSP担任的工作是快速而复杂的核心运算,但是,在运算的同时DSP对数据输入输出的控制是有限的,DSP与CPLD(复杂可编程逻辑器件)或FPGA(现场可编程阵列)相结合的设计则可以有效地弥补这种不足。笔者设计的基于DSP实时视频编解码系统,采用TI(德州仪器)公司的最新高性能低功耗TMS320VC55x系列DSP芯片TMS320VC5509做视频双向编解码运算,但如果DSP还承担视频输入输出的工作,那么视频编解码运算的实时性将得不到保证,因此,这里采用Altera公司的CPLD芯片EP1K50作为视频输入输出的缓冲和控制,DSP与CPLD之间的通信采用McBSP串口(多通道缓冲串口)DMA方式。

2 CPLD的内部结构设计

数据输入通道是由视频采样芯片SAA7114H、CPLD和C5509的McBSP串口组成,视频采样数据从SAA7114H出来之后,在CPLD的内部输入FIFO(先入先出队列)中缓冲一下,由于McBSP是串行的,所以在CPLD内部要进行并串转换,串行输出,同时还要产生同步时钟给McBSP串口。

数据输出通道是由McBSP串口、CPLD和LCD(液晶)控制器组成,解码后的视频数据经过McBSP串行进入CPLD,在其内部串并转换之后,送入内部的输出FIFO暂时缓存一下,然后进入外部的LCD控制器

关键词:McBSP,CPLD,VHDL,DSP

在许多数字信号处理应用系统中,DSP担任的工作是快速而复杂的核心运算,但是,在运算的同时DSP对数据输入输出的控制是有限的,DSP与CPLD(复杂可编程逻辑器件)或FPGA(现场可编程阵列)相结合的设计则可以有效地弥补这种不足。笔者设计的基于DSP实时视频编解码系统,采用TI(德州仪器)公司的最新高性能低功耗TMS320VC55x系列DSP芯片TMS320VC5509做视频双向编解码运算,但如果DSP还承担视频输入输出的工作,那么视频编解码运算的实时性将得不到保证,因此,这里采用Altera公司的CPLD芯片EP1K50作为视频输入输出的缓冲和控制,DSP与CPLD之间的通信采用McBSP串口(多通道缓冲串口)DMA方式。

1 McBSP的硬件接口及时序分析

TMS320VC5509是TI公司生产的第三代高性能低功耗DSP芯片,有三个McBSP串口,McBSP串口是在标准同步串口基础上的功能扩展,提供了强大的同步串口通信机制,速度可达100Mbit/s,具有以下特征:

·全双工通信;

·双缓存的发送寄存器和三缓存的接收寄存器,允许连续的数据流传输;

·为数据发送和接收提供独立的帧同步脉冲和时钟信号;

·能够发送中断给CPU,发送事件信号给DMA控制器;

·发送和接收各有128个通道,可以允许或阻断某个通道的传输;

·数据长度可以为8、12、16、20、24、32;

·提供了A-律和μ-律压缩扩展;

·内部时钟和帧同步信号的可编程性;

·与T1/E1、SPI、AC97、I2S等直接接口。

2 CPLD的内部结构设计

数据输入通道是由视频采样芯片SAA7114H、CPLD和C5509的McBSP串口组成,视频采样数据从SAA7114H出来之后,在CPLD的内部输入FIFO(先入先出队列)中缓冲一下,由于McBSP是串行的,所以在CPLD内部要进行并串转换,串行输出,同时还要产生同步时钟给McBSP串口。

数据输出通道是由McBSP串口、CPLD和LCD(液晶)控制器组成,解码后的视频数据经过McBSP串行进入CPLD,在其内部串并转换之后,送入内部的输出FIFO暂时缓存一下,然后进入外部的LCD控制器

模拟电路 模拟芯片 德州仪器 放大器 ADI 模拟电子 相关文章:

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- PIC16C5X单片机睡眠状态的键唤醒方法(11-16)

- 用简化方法对高可用性系统中的电源进行数字化管理(10-02)

- 利用GM6801实现智能快速充电器设计(11-20)