高阶滤波器的设计实例

实现高阶滤波器的方法是把基高阶函数分解成多个二阶因式之积,每个二阶因式用对应的二阶滤波器来实现,将这些二阶滤波器串接起来即是所需的高阶滤波器。这样,就把设计复杂的高阶滤波器的问题简化为二阶节基本单元设计。

设计举例:

例如,设计截止频率为1000HZ的低通滤波器,要求通带幅频响应平坦。截止频率以外的下降率为100DB/10倍频。

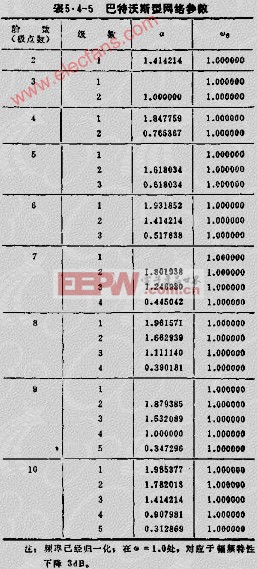

显然,选择五阶巴特沃斯LPF,其框图如图5.4-59A所示。由一级和两级二阶电路组成。巴特沃斯型网络参数见表5.4-5。

1)已知条件WO、A和HO的确定,由表5.4-5查得N=5时有WO=WO1=WO2=WO3=1.000000。A2=1.618034,A3=0.618034。

选择HO=1

这里,频率已经归一化。由此可求得各级实际截止频率为

WC=WO=WO1=WO2=WO3=2πFC=6280/S

对巴特沃斯LPF有WC和WO相等

2)确定电路形式及计算各级R和C的数值

既可选择VCVS型LPF,也可选择MFB型的LPF的具体电路来实现设计的要求。

本例选择VCVS型的LPF。

在计算R和C的数值时,既可先任选定C,也可先任选定R。本例选定各级RC网络中的R均等于10K。

第一级的已知条件是WO=6.28/NS,R=10K,HO=1。即可求出此级C=0.0159UF。

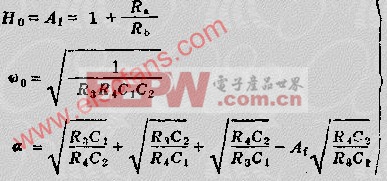

第二级的已知条件是WO=6.28/NS,A2=1.618034,HO=1,R=10K。代入式(见下式),即可求出此级的C3=0.01967UF,C4=0.01288UF。

第三级的已知条件是WO=6.28/,A8=0.618034,HO=1,R=10K。代入式:

即可求出第三级的C2=0.05150UF,C4=0.004918UF。

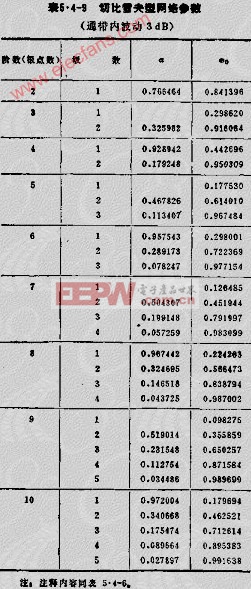

由此则设计出如图5.4-59B所示的VCVS型五阶LPF。表5.4-6~表5.4-10示出了切比雪夫和贝塞尔网络参数。

在实际应用中,要求能快速、简便的设计或选用具有一定精度,能满足工程上要求的滤波器。因而在工程上,都采用直接查表法设计所需的滤波器。

制作有源滤波器时,设计者要选用在GB积和SR均能满足要求的运算放大器。一般要求FCGB/50,对截止频率和中心频率高的滤波器应选用SR大的集成运放。特别是在高通滤波器中,往往由于SR不够高,会产生严重波形失真,或者Q值下降。再者,电路中的无源元件的变化对电路的灵敏度有很大影响,因此对低阶滤波器,要求电阻容差为5%,对五阶和六阶要求电阻容差为2%,对七阶和八阶要求电阻容差为1%。对电容,因价格的问题,在低阶情况下,要求其容差为10%即可,对更高阶次,当然选用和电阻相当容差是令人满意的。但是要求应适当放宽。另外,还对运放噪声等指标,有一定的要求。

在设计出一个有源滤波器的实际电路以后,还需进行最后的调整。即调整元件的数值和增益,以补偿元件的公差和寄生效应。

密Q值滤波器

前面所求的滤波器都不适合于实现高Q值网络函数。实现高Q值的电路,在电路结构上的复杂性大大地增加了。如图5.4-60所示的是一双二次型二阶低通滤波器,其Q值可高达100。至于其他高Q值电路。

- 无需调谐的“砖墙式”低通音频滤波器(11-20)

- 视频有源滤波器 (11-26)

- 通用和低噪声的有源滤波器提供达10MHz的可重复性能(01-05)

- 直流耦合视频放大器/滤波器的视频信号电平转换(07-03)

- 开关电容梳状滤波器幅频特性的深入分析(06-05)

- 在高温超导滤波器后级的低温低噪声放大器的设计和调试方法(06-01)