基于ADS的S波段平衡式宽带低噪声放大器设计

2.3.2 源极反馈电路的设计

一般的放大器网络为共源极结构,栅极为输入端,漏极为输出端。放大器能正常工作的前提是电路是稳定的,即稳定因子K>1。改善放大器稳定性的途径有在栅极加串联电阻和增加反馈电路等。在栅极加串联电路虽然可以增加稳定性,但恶化了噪声系数,而源极负反馈因为不涉及电路的信号通路,所以对放大网络噪声的影响很小。通过给晶体管加入源极负反馈,可以改善晶体管的稳定状态。通常源极负反馈都是加入电感性元件。但是电感值通常太小,所以不用集总元件实现,而是使用终端短路微带线来实现。该设计采用源极加终端短路微带线的方式,通过ADS仿真可以较为准确的评估晶体管的稳定性。

2.3.3 输入/输出匹配设计和仿真

在设计匹配网络的时候,选择合理的拓扑结构对于低噪声放大器的设计至关重要。本文采用的拓扑结构是并联导纳式结构,即利用串联微带传输线进行导纳变换,然后并联一个微带分支线,微带线的终端开路(或短路),用其输入导纳作为补偿电纳,以达到电路匹配。因为是最前端的低噪声放大器,所以输入端匹配电路按照最小噪声系数进行匹配,当ΓS=Γopt时,噪声系数最小,NF=NFmin。当ΓS≠Γopt时,

选取等噪声系数圆上的最佳噪声系数点的阻抗做输入端匹配。输入端匹配完成之后,输出端匹配按照最大增益进行匹配。在ADS里可以进行原理图和版图仿真的调谐和优化。因为频带内增益平坦度也是一个重要指标,所以在设计的过程中增益平坦度和噪声系数之间需要做一个折中和妥协。分支LNA的版图如图4所示。

ADS中可以把layout中的无源电路和原理图中的元器件有机结合在一起进行联合仿真,既考虑到了版图的场的效应,又考虑到原理图中有源器件和集总元件的路的效应。这样仿真结果和实测结果可以非常接近,大大缩短制版调试的周期。由仿真结果可以得出:分支LNA的增益达到了10.6 dB,频带内增益平坦度小于0.5 dB,噪声系数小于1.003 dB,稳定性系数K在1.02~1.06之间。放大器为无条件稳定。因为设计中使用的为ATF54143的Spice模型,因此在ADS中可以作谐波仿真。由仿真结果可得,分支LNA的输出P1 dB压缩点为17.7 dBm,此时输入功率为8.5 dBm。由ATF54143的芯片资料可得,该晶体管的输出1 dB压缩点约为20.4 dBm。因为电路采用晶体管源极负反馈以及宽带低噪声匹配牺牲了部分增益,所以电路的1 dB压缩点有约2 dB多的下降。

2.4 90°宽带功分器的仿真和版图设计

在S波段,通常的90°分支线耦合器和Wilkinson功分器要做到3~4 GHz的带宽和较好的性能需要采用两级或更多,尺寸会较大(3~4 GHz两级分支线耦合器在RO4003射频板上的尺寸达到了10 mm×20 mm)。而Wilkinson功分器要达到宽带性能也要牺牲尺寸,并且还需要解决一个宽带90°微带延长线的问题。而采用MiniCircuits公司的QCS-442+90°宽带功分器,在电性能较好的同时可以有很小的尺寸,这给平衡式放大器的设计带来了新的思路。

为了验证QCS-442+90°功分器的性能,在ADS里用QCS-442+90°功分器的S参数模型进行原理图版图联合仿真,如图5所示。

2.5 平衡式放大器的版图设计和联合仿真

将90°宽带功分器和分支放大器的版图合在一起,进行原理图-版图的co-simulation,如图6所示。

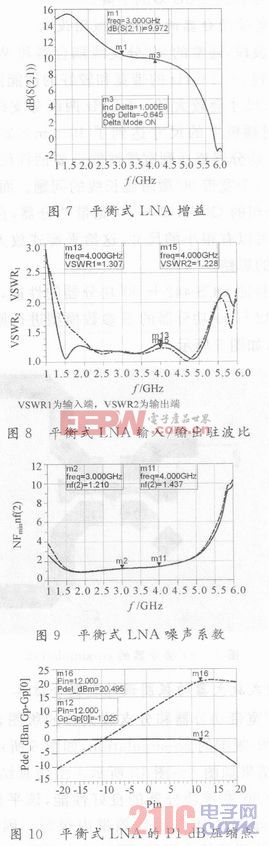

仿真结果如图7~图10所示。由仿真结果可以得出,受益于90°宽带功分器的良好性能,该平衡式LNA的输入/输出驻波比在设计频带内很好。因为输入端90°宽带功分器的插入损耗,所以放大器增益减小,噪声系数增大,但也都在可接受的范围之内。用谐波平衡法仿真该平衡式放大器的P1 dB压缩点等性能。仿真结果如图10所示。

由图10可知,该LNA的输入1 dB压缩点为12 dBm,输出1 dB压缩点为20.5 dBm。正好比每个分支的LNA的P1 dB值大3 dB。

3 结语

低噪声放大器设计主要考虑的指标是放大器噪声系数和增益,但是这通常会牺牲放大器输入驻波比的性能。并且低噪声放大器为晶体管小信号放大,动态范围较小,又在雷达接收通道的最前端,很容易因为外来的大信号而饱和。平衡式放大器能够在增加一定的噪声系数和损失一定的增益的条件下较好的改善输入/输出驻波比,同时平衡式低噪声放大器的功率容量比单路放大器大一倍,可以有效增大接收机的动态范围。高电子迁移率晶体管具有良好的噪声和增益特性,是设计低噪声放大器的较好选择。同时随着制造技术的提高,新型90°宽带功分器能够比通常的微带形式的耦合器有更小的体积,给相应频段的平衡式放大器带来了新的设计思路。Agilent的ADS是功能强大的射频微波仿真平台,可以提供丰富且精确的器件仿真模型,使得设计更加贴合实际的电路。在射频微波电路的设计中使用ADS软件防真可以在设计中预先对电路的性能进行较为精确的优化和评估,减小实际电路制造中的风险,缩短研发周期,节约研发成本。

本文给出了基于ATF54143的S波段平衡式低噪声放大电路的设计、仿真分析。仿真结果表明,所设计的低噪声放大器在3~4 GHz,噪声系数大小于1.5 dB,增益为(9.6±0.3)dB,输入/输出驻波比不大于1.3,输出1 dB压缩点为20.5 dBm。

- 稳定低噪声放大器中晶体管工作点的设计方法(下)(11-20)

- 24位高精度模数转换器ADSl258的原理应用(11-28)

- 用ADS实现一个2.38GHz全集成化低噪声放大器设计(04-26)

- 基于ADS8364的数据采集系统设计(10-01)

- 发夹型滤波器的设计(10-23)

- 基于ADS1255的地震信息采集模块设计(12-01)