2.可在上、下区域工作的LLC谐振转换器的设计

步骤1. 选择m 和 fr ,并计算Mfr

利用式2,谐振频率fr 下的谐振增益Mfr 可由下式求得:

式3

上式中,m 和 fr 都由设计人员选择。若选择的m值很小,峰值增益增加,且需要较大的Lr。若m值过小,需要外部电感,因为这时要在集成式变压器中获得高值 Lr 实际上是相当困难的。另一方面,如果选择较大的m值,则峰值增益降低。由于Lr 比 Lp低,使用集成式变压器十分容易。一般而言,m值在4-7之间是比较合理的。

[设计实例]

当 m 和 fr 分别设置为 6 和 100 kHz时,求得谐振频率下的谐振增益为1.09。

步骤2. 确定最大增益

利用下列公式可求出所需最小和最大增益:

式4

这里,Mmin 和 Mmax 分别为最小和最大增益。Vvirtual 是对应于谐振频率的有效输入电压。

如前所述,如果谐振电压下的Vvirtual 被设定为大于最大输入电压Vin,max,则工作频率将总是低于谐振频率,于是设计出的LLC谐振转换器就会工作在下谐振工作区域。

[设计实例]

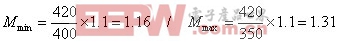

假定Virtual 设为420 Vdc并考虑到余裕,Mmin 和 Mmax 可采用式4计算:

考虑到因负载瞬态和输入电压变化,峰值增益应具有一定余裕,增加10%的余裕是比较恰当的,故合理的Mmax 为 1.45。

步骤3. 确定集成式变压器的匝数比

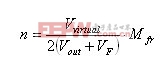

利用步骤2中求得的有效输入电压Vvirtual 和合理的谐振增益Mfr ,集成式变压器的匝数比可由下式求得:

这里,Vout 和 VF分别是次级端二极管的额定输出电压和正向电压降。

如果需要调节匝数比n,可回到步骤2,增加或减小有效输入电压Vvirtual即可。

[设计实例]

在步骤2中,Vvirtual 已被设为420 Vdc。VF 取1Vdc,集成式变压器的匝数比算得为:

步骤4. 确定谐振网络

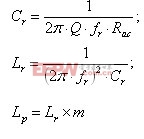

利用图5所示的这种查找表,能够根据峰值增益和不同的m值找出正确的Q因子。利用m值和前面步骤中获得的所需最大增益,可在图5中选出正确的Q因子。一旦确定了正确的Q因子,谐振网络的参数就可利用下面的公式求出

这里,Cr 和Lr 分别为谐振电容和电感,Lp 为集成式变压器的初级端电感。Rac 等于,其中考虑到了次级端二极管的正向电压降。

这里,Cr 和Lr 分别为谐振电容和电感,Lp 为集成式变压器的初级端电感。Rac 等于,其中考虑到了次级端二极管的正向电压降。

[设计实例]

在前面的步骤中,m值选为6,考虑到了余裕的所需最大增益 Mmax 求得为1.45。通过图5找出的Mmax对应的正确Q因子为0.35。

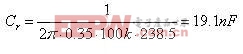

当谐振频率为100 kHz时,谐振电容Cr 的值可由下式求出:

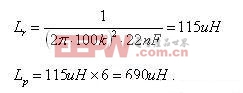

考虑到出厂电容的标准值,一个22nF的电容就足够了。Lr 和 Lp 谐振电感的值可由下式求出:

后续的设计步骤和更多的技术信息

本文简单介绍了下谐振工作及其LLC谐振参数的设计步骤。不过,尚未提及选择谐振参数之后的若干设计步骤,比如集成式变压器的设计,开关的额定电压和电流、二极管和谐振电容的选择,以及控制器和反馈电路的设计。

- LLC 串联谐振变换器 FSFR2100(02-12)

- 如何实现高功率密度的工业电源(05-10)

- 满足高性能和功效要求的单芯片CCM PFC及LLC组合控制器NCP1910(10-28)

- 挑战对离线LED拓扑的选择(01-14)

- 一种高转换效率高功率因素的大功率LED电源研究(03-08)

- 宽电压输入半桥型LLC谐振变换器设计与实验(03-12)